•

writel(value, address);

2.

readl

to read from HPS register

•

readl(address);

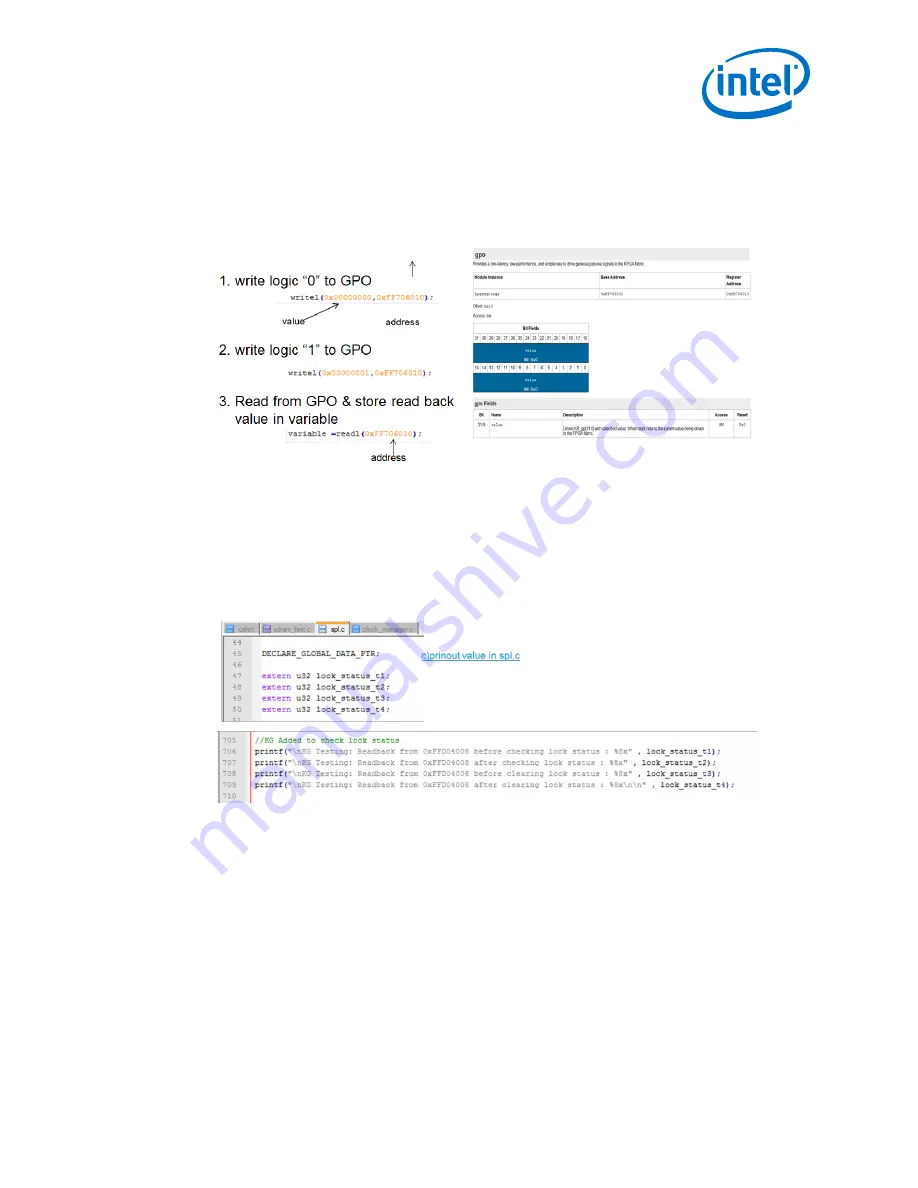

For example:

5.4.1.7. Check HPS PLL Lock Status in Preloader

•

Read HPS PLL Status Register in

clock_manager.c

and print out in

spl.c

— Define global variable in

clock_manager.c

and “extern variable” in

spl.c

— Unable to printout value in

clock_manager.c

as the UART has not been

initialized yet

5.4.2. Access HPS SDRAM via the FPGA-to-SDRAM Interface

The HPS bridges can be enabled from the Preloader (SPL/MPL) or U-Boot and in some

cases from Linux.

Note:

Preloaders (SPL) and U-Boot generated from SoC EDS 13.1 and later contain extra

functionality and built in functions to safely enable the HPS bridges.

To enable the HPS FPGA-to-SDRAM bridge from the Preloader or U-Boot, follow the

appropriate steps.

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

67