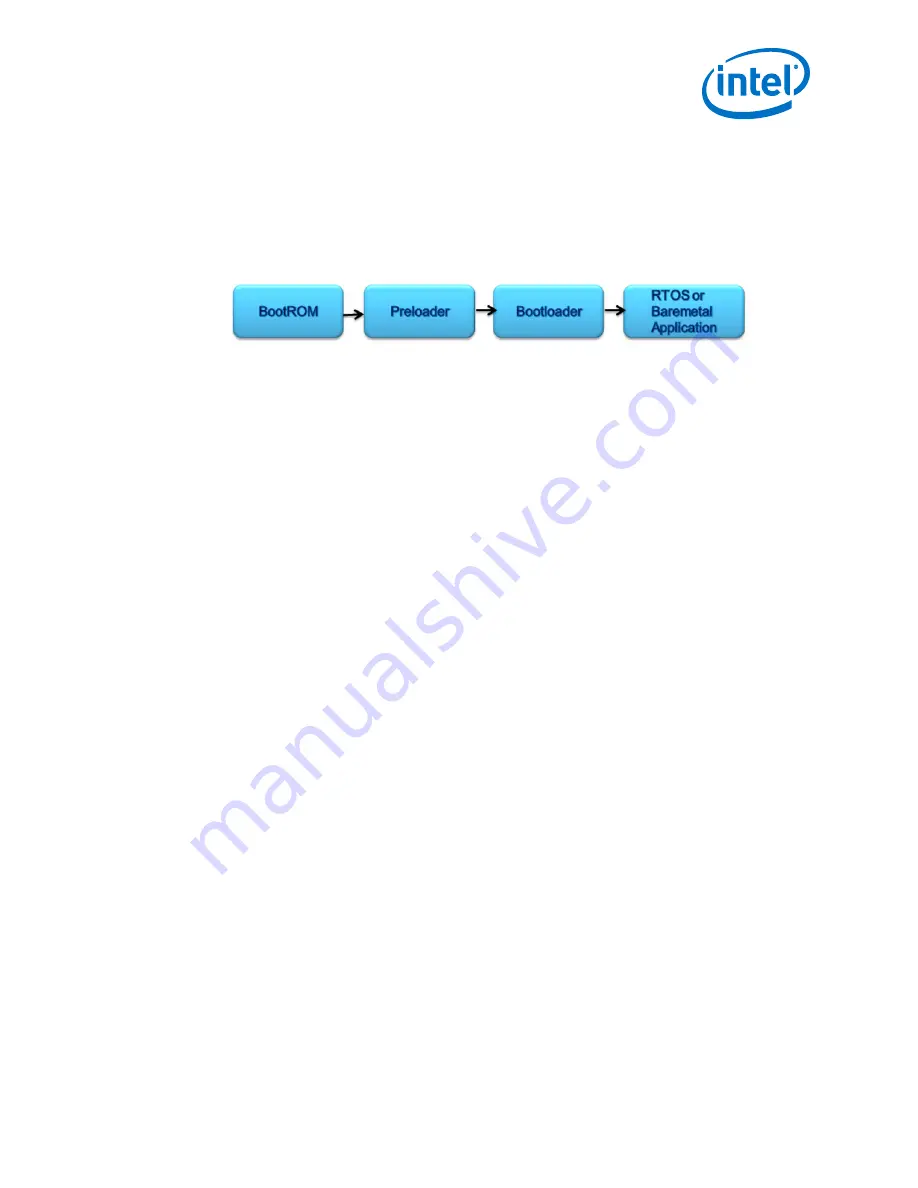

1. Boot ROM

2. Preloader

3. Bootloader

4. Real-time operating system or bare-metal application

Figure 13.

Cyclone V / Arria V SoC Boot Flow

The BootROM and Preloader stages are needed for all Cyclone V SoC / Arria V SoC

applications. U-boot and Linux are used by the GSRD, but a custom application may

implement a different flow, such as using the Preloader to load a bare-metal

application directly.

Typically, the main responsibilities of the Preloader are:

•

Perform additional HPS initialization

•

Bring up SDRAM

•

Load the next boot stage from Flash to SDRAM and jump to it

Currently, two different Preloader options are available:

•

SPL - part of U-Boot. Provided with SoC EDS under GPL (Open Source) License

•

MPL - provided with SoC EDS as an example using the HWLibs (bare-metal

libraries). Uses BSD license.

Note:

The Preloader requires a special header to be placed at the beginning of the next

stage boot image. Also, the header contains a CRC value used to validate the image.

The header can be attached to an image by using the mkimage utility that is included

with SoC EDS.

The Bootloader has typical responsibilities that are similar with the Preloader, except it

does not need to bring up SDRAM. Because the Bootloader is already residing in

SDRAM, it is not limited by the size of the OCRAM. Therefore, it can provide a lot of

features, such as network stack support.

A typical HPS system had numbers of registers that need to be set for a given

configuration of the MPU subsystem, the network-on-chip interconnect component, the

SDRAM memory, flash boot source and peripheral interfaces. The settings used for

boot or initialization purposes are encapsulated in the following places:

•

RBF File(s) - containing register settings for SDRAM also dedicated I/O and FPGA

pin configuration.

•

U-Boot source code - for rest of the settings

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

59