Document Number: 002-14826 Rev. *G

Page 9 of 65

PRELIMINARY

CYW43903

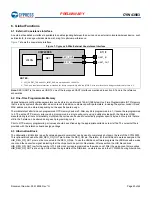

Figure 3. Typical Power Topology (Page 1 of 2)

VBAT

1.35V

CYW43903 1.2V

REG_ON

Core Buck

Regulator

(CBUCK)

LPLDO1

CLDO

VDDIO

XTAL LDO

Cap-less

LNLDO

Cap-less

LNLDO

Cap-less

VCOLDO

Cap-less

LNLDO

Cap-less

LNLDO

1.2V

APPS Subcore

APPS SOCSRAM

APPS VDDM

WL VDDM (SRAMS in AOS)

WL Subcore

WL PHY

WLAN/CLB/Top, Always On

1.3V, 1.2V,

.095V (AVS)

WLRF RFPLL, PFD, and MMD

1.35V

WLRF XTAL

WLRF ADC REF

WLRF TX

WLRF AFE and TIA

WLRF LNA

WLRF LOGEN

WLRF TX Mixer and PA (not always)

1.2V

1.2V

1.2V

1.2V

1.2V

Mini‐PMU

(Inside WL Radio)

15 mA

VBAT

Operational:

2.3V to 4.8V

Performance:

3.0V to 4.8V

Absolute Maximum: 5.5V

VDDIO

Operational:

3.3V

Supply ball

Supply bump/pad

Ground ball

Ground bump/pad

External to chip

Power

switch

No power switch

No dedicated power switch, but internal power‐

down modes and block‐specific power switches

WLAN reset

ball

BBPLL

LNLDO

WL BBPLL/DFLL

1.2V