Rev. 1.00

96

��ne ��� �01�

Rev. 1.00

9�

��ne ��� �01�

HT66FM5440

Brushless DC Motor A/D Flash MCU

HT66FM5440

Brushless DC Motor A/D Flash MCU

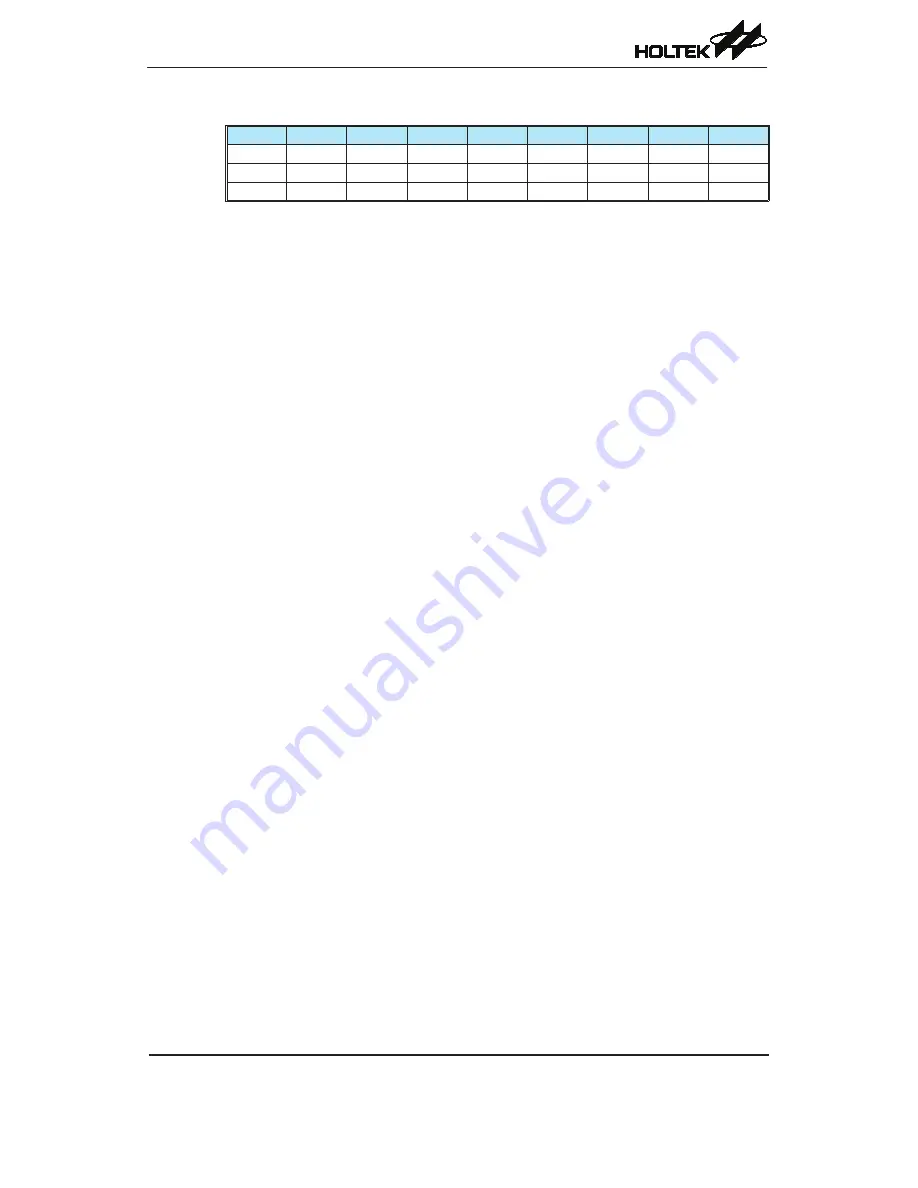

• ADCR1 Register

Bit

7

6

5

4

3

2

1

0

Name

ADRE

DLSTR

PWIS

ADCHVE ADCLVE

ADCK�

ADCK1

ADCK0

R/W

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7

ADRE

: ADSTR triggered A/D conversion interrupted by A/D auto-scan flag

0

: ADSTR triggered A/D conversion interrupted by A/D auto-scan has not occurred

1: ADSTR triggered A/D conversion interrupted by A/D auto-scan has occurred

As the A/D auto-scan triggered conversion has a higher priority than the ADSTR

triggered A/D conversion, it can interrupt an ongoing ADSTR triggered A/D

conversion. The ADRE bit can be used to monitor whether such condition has

occurred. If yes, this bit will be set high by hardware to indicate that the current

ADSTR triggered A/D conversion is incompleted and the result in the ADRH and

ADRL register pair is invalid.

Bit 6

DLSTR

: A/D auto-scan conversion control

0: Disable, A/D auto-scan conversion off

1: Enable, A/D auto-scan conversion on

Setting this bit high will enable an A/D auto-scan triggered A/D conversion which can

interrupt the current ADSTR triggered A/D conversion since it has a higher priority

than the latter.

Bit 5

PWIS

: Select PWM source to trigger A/D auto-scan

0: Select PWM period to trigger auto-scan

1: Select PWM duty to trigger auto-scan

When this bit is set high to select PWM duty to trigger auto-scan conversion, the

detailed PWM duty source is furtherly determined by the PWDIS1~PWDIS0 bits in

the ADCR2 register.

Bit 4~3

ADCHVE, ADCLVE

: A/D compare interrupt trigger source selection

00: Low boundary value

<

Converted data

<

High boundary value

01: Converted data

≤

Low boundary value

10: Converted data

≥

High boundary value

11: Converted data

≤

Low boundary value or Converted data

≥

High boundary value

The low boundary value is the content in the ADLVDH and ADLVDL register pair, the

high boundary value is the content in the ADHVDH and ADHVDL register pair. The

converted data indicates the converted result of OPA0O, OPA1O and OPA2O, which

are stored in ADRH and ADRL register pair or ISRHn and ISRLn register pair. When

the preset compare interrupt source condition occurs, an A/D converter boundary

interrupt will be generated.

Bit 2~0

ADCK2~ADCK0

: A/D conversion clock source select

000: f

SYS

001: f

SYS

/2

010: f

SYS

/4

011: f

SYS

/8

100: f

SYS

/16

101: f

SYS

/32

110: f

SYS

/64

111: Undefined

These three bits are used to select the clock source for the A/D converter.