Rev. 1.00

1��

��ne ��� �01�

Rev. 1.00

1�9

��ne ��� �01�

HT66FM5440

Brushless DC Motor A/D Flash MCU

HT66FM5440

Brushless DC Motor A/D Flash MCU

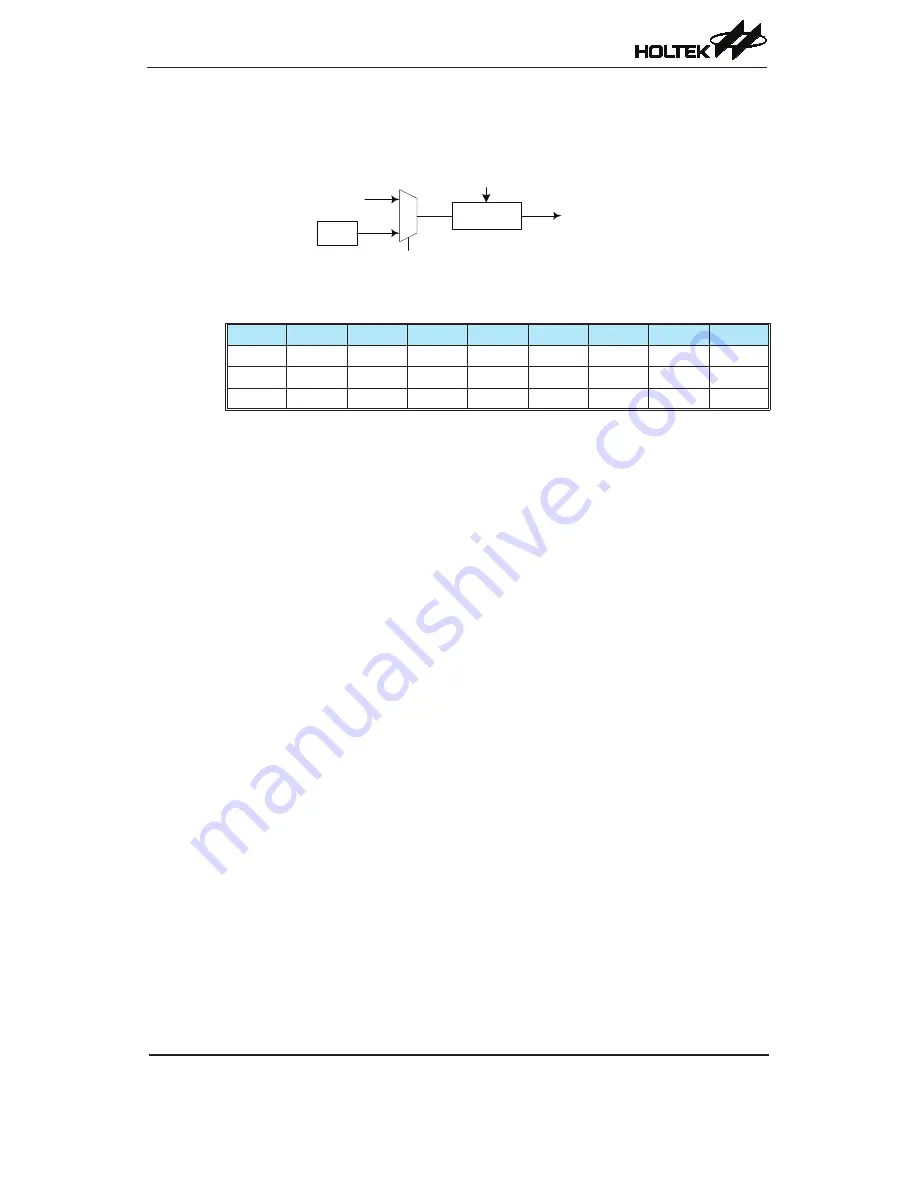

The Time Base clock source, f

TB

, originates from the internal clock source f

SYS

/4 or f

TBC

and then

passes through a divider, the division ratio of which is selected by programming the TB

1

and TB

0

bit

s to obtain longer interrupt periods whose value ranges.

M

U

X

f

SYS

/4

f

TBC

÷�

1�

~�

15

TBCK

f

TB

Time Base Interr�pt

TB1~TB0

LIRC

Time Base Interrupt

TBC Register

Bit

7

6

5

4

3

2

1

0

Name

TBON

TBCK

TB1

TB0

—

—

—

—

R/W

R/W

R/W

R/W

R/W

—

—

—

—

POR

0

0

1

1

—

—

—

—

Bit 7

TBON

: Time Base Control

0: Disable

1: Enable

Bit 6

TBCK

: Select f

TB

clock

0:

f

TBC

1:

f

SYS

/4

Bit 5~4

TB1~TB0

: Select Time Base Time-out Period

00:

f

TB

/2

12

01:

f

TB

/2

13

10:

f

TB

/2

14

11:

f

TB

/2

15

Bit 3~0

Unimplemented, read as "0"

LVD Interrupt

The Low Voltage Detector Interrupt is contained within the multi-function

i

nterrupt 7 sharing the

same interrupt number with other interrupt sources in the same group. After being configured with

the desired interrupt priority level, an LVD Interrupt request will take place when the LVD Interrupt

request flag, LVF, and the associated interrupt priority request flag

are

set, which occurs when the

Low Voltage Detector function detects a low power supply voltage. To allow the program to branch

to its respective interrupt vector address, the global interrupt enable bit, EMI, Low Voltage Interrupt

enable bit, LVE, and associated interrupt priority enable bit must first be set. When the interrupt is

enabled, the stack is not full and a low voltage condition occurs, a subroutine call to

its

i

nterrupt

vector will take place. When the Low Voltage Interrupt is serviced, the EMI bit will be automatically

cleared to disable other interrupts, however only the interrupt priority request flag will be also

automatically cleared. As the LVF flag will not be automatically cleared, it has to be cleared by the

application program.