ETAS

Technical Data

ETK-S20.1

-

User Guide

41

7.11

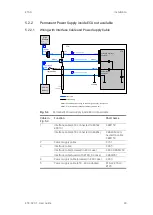

DAP Timing Characteristics

The following diagrams show the timings the ETK-S20.1 can process.

7.11.1

DAP Timing Diagram

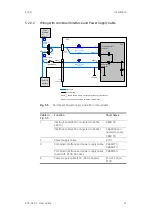

7.11.2

DAP Timing Diagram DAP Timing Parameter

NOTE

DAP timing parameters in this chapter refer to the DAP interface (CON1/

CON6) of the ETK-S20.1. The DAP wiring to the ECU (ETAF1/ ETAL1) must be

taken account additionally.

All timings are measured at a reference level of 1.5 V. Output signals are mea

-

sured with 20

pF to ground and 50

to 1.5

V.

Parameter

Symbol

Value [ns] Comment

DAP0 Clock Period

(ETK --> Target)

t

CLK

10

100 MHz DAP Clock Fre

-

quency

20

50 MHz DAP Clock Frequency

DAP1 Set-Up Time

(ETK --> Target)

t

SU

4

DAP1 Hold Time

(ETK --> Target)

t

H

2

DAP1 Clock-to-Out

Time (Target --> ETK)

t

CO

~

Undetermined, ETK automati

-

cally determines optimum

sampling point

DAP1 Valid Window

(Target --> ETK)

t

Valid

8

DAP0_(ETK)

DAP1_(ETK)

DAP1_(ECU)

t

SU

t

H

t

Valid

t

CLK

t

CO