12 I

2

C (I2C)

S1C17F13 TeChniCal Manual

Seiko epson Corporation

12-11

(Rev. 1.0)

Data sending operations

START condition detection and slave address check

While the I2C

n

CTL.MODEN bit = 1 and the I2C

n

CTL.MST bit = 0 (slave mode), the I2C Ch.

n

monitors

the I

2

C bus. When the I2C Ch.

n

detects a START condition, it starts receiving of the slave address sent from

the master. If the received address is matched with the own address set to the I2C

n

OADR.OADR[6:0] bits

(when the I2C

n

MOD.OADR10 bit = 0 (7-bit address mode)) or the I2C

n

OADR.OADR[9:0] bits (when the

I2C

n

MOD.OADR10 bit = 1 (10-bit address mode)), the I2C

n

INTF.STARTIF bit and the I2C

n

INTF.BSY bit

are both set to 1. The I2C Ch.

n

sets the I2C

n

INTF.TR bit to the R/W bit value in the received address. If this

value is 1, the I2C Ch.

n

sets the I2C

n

INTF.TBEIF bit to 1 and starts data sending operations.

Sending the first data byte

After the valid slave address has been received, the I2C Ch.

n

pulls down SCL to low and enters standby

state until data is written to the I2C

n

TXD register. This puts the I

2

C bus into clock stretching state and the

external master into standby state. When transmit data is written to the I2C

n

TXD register, the I2C Ch.

n

clears the I2C

n

INTF.TBEIF bit and sends an ACK to the master. The transmit data written in the I2C

n

TXD

register is automatically transferred to the shift register and the I2C

n

INTF.TBEIF bit is set to 1. The data

bits in the shift register are output in sequence to the I

2

C bus.

Sending subsequent data

If the I2C

n

INTF.TBEIF bit = 1, subsequent transmit data can be written during data transmission. If the

I2C

n

INTF.TBEIF bit is still set to 1 when the data transmission from the shift register has completed, the I2C

Ch.

n

pulls down SCL to low (sets the I

2

C bus into clock stretching state) until transmit data is written to the

I2C

n

TXD register.

If the next transmit data already exists in the I2C

n

TXD register or data has been written after the above,

the I2C Ch.

n

sends the subsequent eight-bit data when an ACK from the external master is received. At the

same time, the I2C

n

INTF.BYTEENDIF bit is set to 1. If a NACK is received, the I2C

n

INTF.NACKIF bit is

set to 1 without sending data.

STOP/repeated START condition detection

While the I2C

n

CTL.MST bit = 0 (slave mode) and the I2C

n

INTF.BSY = 1, the I2C Ch.

n

monitors the I

2

C

bus. When the I2C Ch.

n

detects a STOP condition, it terminates data sending operations. At this time, the

I2C

n

INTF.BSY bit is cleared to 0 and the I2C

n

INTF.STOPIF bit is set to 1. Also when the I2C Ch.

n

detects a

repeated START condition, it terminates data sending operations. In this case, the I2C

n

INTF.STARTIF bit is

set to 1.

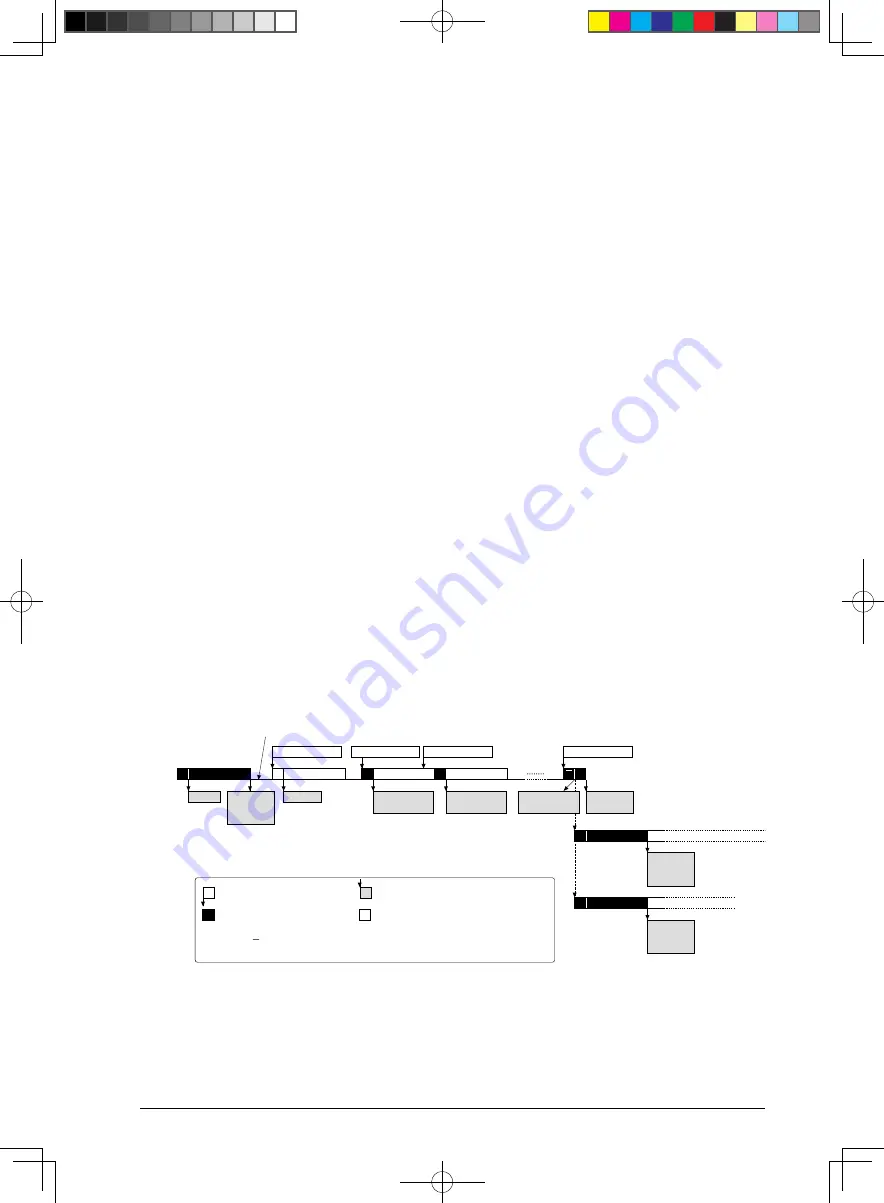

S

P

A

TBEIF = 1

TBEIF = 1

BYTEENDIF = 1

TBEIF = 1

BYTEENDIF = 1

BSY = 0

STOPIF = 1

Saddr/R

A

Data 1

A

Data 2

A

Data 3

I

2

C bus

Clock stretching by I2C

BSY = 1

STARTIF = 1

TBEIF = 1

NACKIF = 1

BYTEENDIF = 1

Sr

Saddr/R

TR = 0

BSY = 1

STARTIF = 1

Sr

Saddr/W

Data 1

→

TXD[7:0]

Data 2

→

TXD[7:0] Data 3

→

TXD[7:0]

Data N

→

TXD[7:0]

Data transmission continued

Data reception starts

Software bit operations

Operations by the external master

S: START condition, Sr: Repeated START condition, P: STOP condition,

A: ACK, A: NACK, Saddr/R: Slave a R(1), Saddr/W: Slave a W(0),

Data

n

: 8-bit data

Hardware bit operations

Operations by I2C (slave mode)

TR = 1

STARTIF = 1

TBEIF = 1

BSY = 1

4.5.1 Example of Data Sending Operations in Slave Mode

Figure 12.