88

EPSON

E0C88832/88862 TECHNICAL MANUAL

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Programmable Timer)

To accept the subsequent interrupt after interrupt

generation, re-setting of the interrupt flags (set

interrupt flag to lower level than the level indicated

by the interrupt priority registers, or execute the

RETE instruction) and interrupt factor flag reset are

necessary. The interrupt factor flag is reset to "0" by

writing "1".

When the 16-bit mode is selected, the interrupt

factor flag FPT0 is not set to "1" and a timer 0

interrupt cannot be generated. (In the 16-bit mode,

the interrupt factor flag FPT1 is set to "1" by an

underflow of the 16-bit counter.)

At initial reset, this flag is reset to "0".

5.10.11 Programming notes

(1) The programmable timer is actually made to

RUN/STOP in synchronization with the falling

edge of the input clock after writing to the

PRUN0(1) register. Consequently, when "0" is

written to the PRUN0(1), the timer shifts to

STOP status when the counter is decremented

"1". The PRUN0(1) maintains "1" for reading

until the timer actually shifts to STOP status.

Figure 5.10.11.1 shows the timing chart of the

RUN/STOP control.

(4) When the OSC3 oscillation circuit is made the

clock source, it is necessary to turn the OSC3

oscillation ON, prior to using the programmable

timer.

From the time the OSC3 oscillation circuit is

turning ON until oscillation stabilizes, an

interval of several 100

µ

sec to several 10 msec is

necessary. Consequently, you should allow an

adequate waiting time after turning the OSC3

oscillation circuit ON before starting the count

of the programmable timer. (The oscillation

start time will vary somewhat depending on the

oscillator and on external parts. Refer to the

oscillation start time example indicated in

Chapter 7, "ELECTRICAL CHARACTERIS-

TICS".)

At initial reset, OSC3 oscillation circuit is set to

OFF status.

(5) When the 16-bit mode has been selected, be sure

to read the counter data in the order of PTD00–

PTD07 and PTD10–PTD17. Moreover, the time

interval between reading PTD00–PTD07 and

PTD10–PTD17 should be 0.73 msec or less.

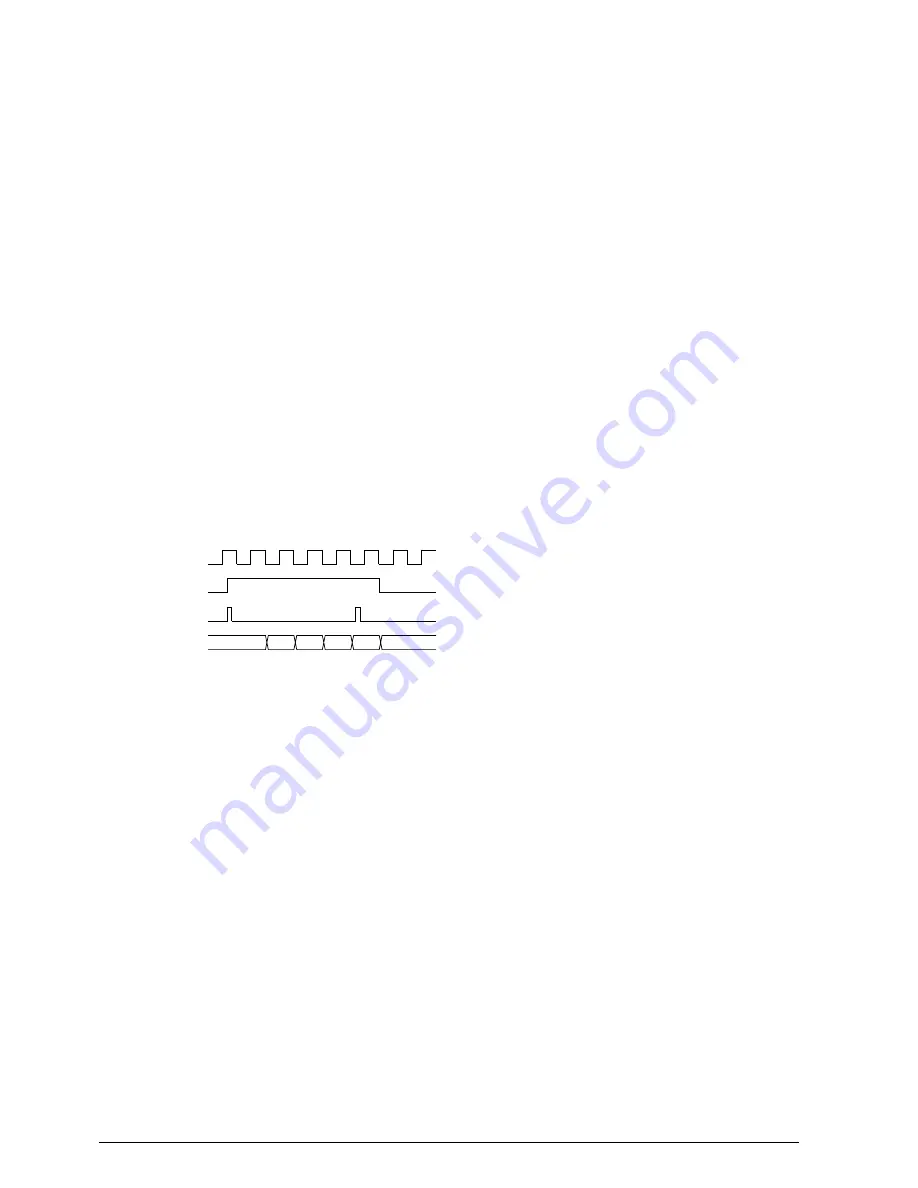

PRUN0/PRUN1(WR)

PTD0X/PTD1X

42H

41H 40H 3FH 3EH

3DH

PRUN0/PRUN1(RD)

Input clock

Fig. 5.10.11.1 Timing chart of RUN/STOP control

The event counter mode is excluded from the

above note.

(2) The SLP instruction is executed when the

programmable timer is in the RUN status

(PRUN0(1) = "1"). The programmable timer

operation will become unstable when returning

from SLEEP status. Therefore, when shifting to

SLEEP status, set the clock timer to STOP status

(PRUN0(1) = "0") prior to executing the SLP

instruction.

In the same way, disable the TOUT signal

output (PTOUT = "0") to avoid an unstable clock

output to the R27 output port terminal.

(3) Since the TOUT signal is generated asynchro-

nously from the register PTOUT, when the

signal is turned ON or OFF by the register

setting, a hazard of a 1/2 cycle or less is gener-

ated.

Содержание 0C88832

Страница 6: ......