3.9.1

Signal Description

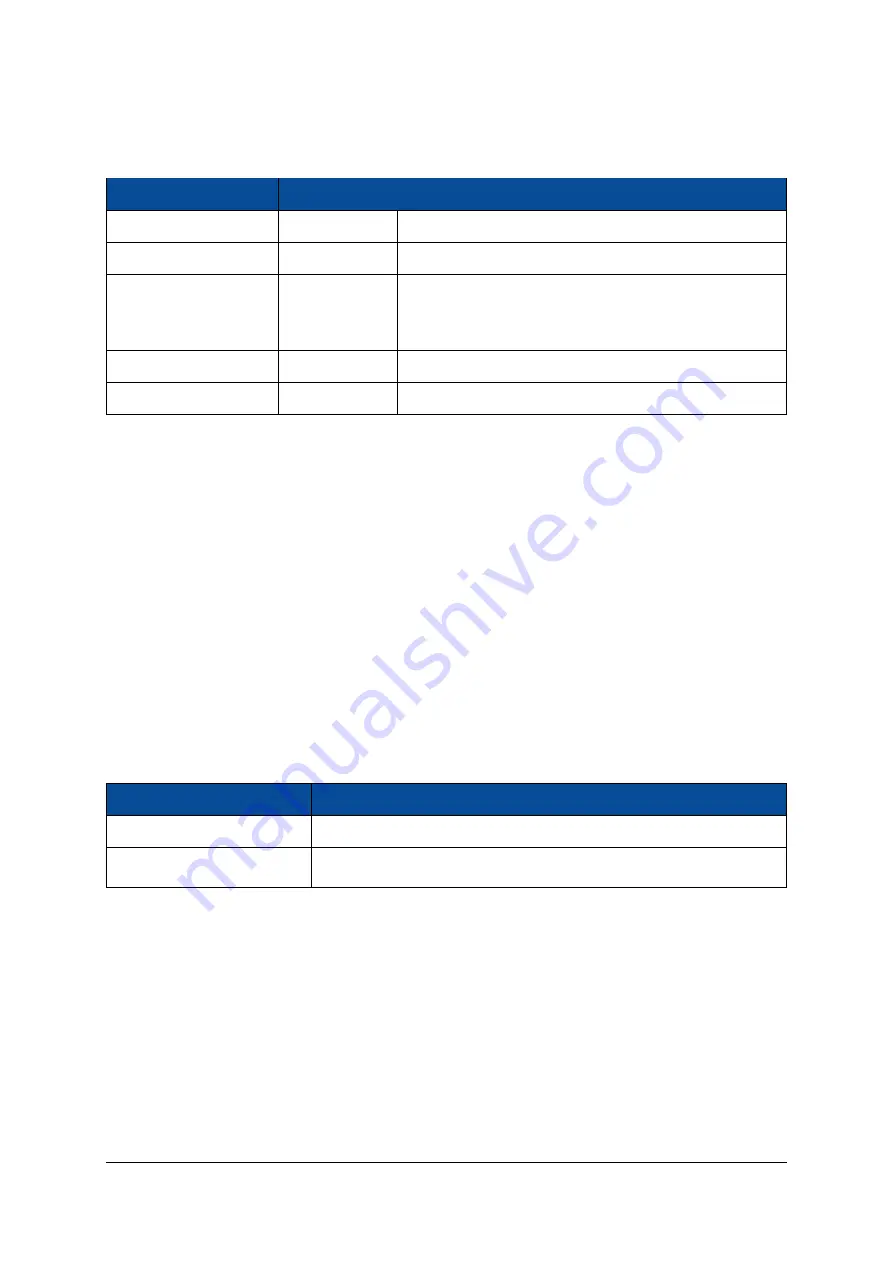

Signal Name

QSPI Flash Pin

Description

FLASH_CLK_FPGA_CCLK

SCK

SPI CLK

FLASH_DO_FPGA_DIN

SO/IO1

SPI MISO

FPGA_PROG#

-

Must be pulled low during QSPI flash programming. When

released, all other pins of the SPI interface must be high

impedance.

FLASH_DI

SI/IO0

SPI MOSI

FLASH_CS#

CS#

SPI CS#

Table 33: Flash Programming from an External Master - Signals Description

3.10

Module Configuration via FTDI USB 2.0 Controller

The FPGA configuration interface and QSPI flash signals are connected to the FTDI USB 2.0 device controller.

This allows FPGA serial configuration and QSPI flash programming over USB from a host computer without

additional hardware.

Port A of the FTDI device can be used in Xilinx JTAG mode or in synchronous FIFO mode to transfer data

between the FPGA and the USB master. The selected configuration is controlled by an FTDI general purpose

I/O; refer to Table 34 for details.

Port B of the FTDI is used to access the module I2C bus and the UART pins of the FPGA, to program the

QSPI Flash or to configure the FPGA in slave serial mode. General purpose I/O pins of port B are used to

control the configuration multiplexers; refer to Table 35 for details.

3.10.1

FTDI Port A Configuration

Port A of the FTDI device can be used for data transfer to a host computer or for Xilinx JTAG implementation.

FTDI_FIFOMODE (BCBUS0)

Port A Mode

0

Xilinx JTAG mode (default mode)

1

FTDI FIFO mode (ADBUS0-7 and ACBUS0-6 are connected to the FPGA)

Table 34: FTDI Configuration Settings - port A

Please note that when using the synchronous FIFO interface, in certain temperature conditions, the timing

path requirement between FPGA and FTDI device is not met.

D-0000-430-002

37 / 48

Version 06, 25.07.2019