Product overview

KL31x2

14

Version: 2.4.0

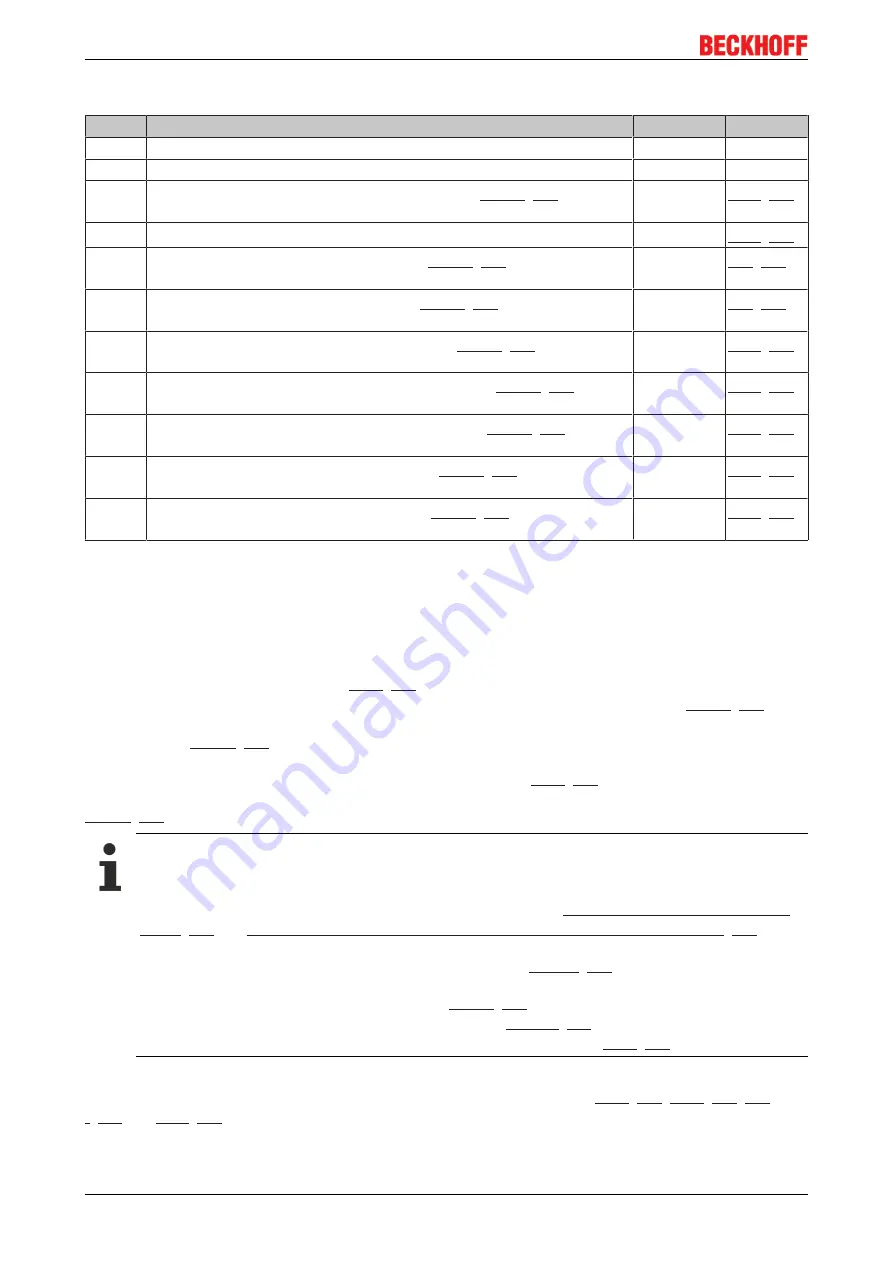

Key

Name

Name

Unit

Register

X

ADC

Output value of the A/D converter

[1]

-

Y

out

Process data for controller

[1]

-

B

A

Vendor calibration: Offset (can be disabled via bit

feature register)

[1]

A

A

Vendor calibration: Gain (always active)

[1 x 2

-16

+ 1]

B

K

Calibration: Offset (can be enabled via bit

of the feature

register)

[1]

A

K

Calibration: Gain (can be enabled via bit

register)

[1]

A

GK

Basic calibration: Gain (can be enabled via bit

of the

feature register)

[1]

B

H

Manufacturer scaling: Offset (can be enabled via bit

feature register)

[1]

A

H

Manufacturer scaling: Gain (can be enabled via bit

of the

feature register)

[1 x 2

-8

+ 1]

B

W

User scaling: Offset (can be enabled via bit

register)

[1]

A

W

User scaling: Gain (can be enabled via bit

register)

[1 x 2

-8

+ 1]

Calibration

The analog channels are self‑calibrated periodically. Analog switches are provided for this purpose, so that

the various calibration signals can be connected. It is important for this process that the entire signal path,

including all passive components, is examined at every phase of the calibration. Only the interference

suppression elements (L/C combination) and the analog switches themselves cannot be examined.

The calibration interval is set in register

in steps of 100 ms. During calibration, no current process

data are present. Value 0 is present. The terminal indicates active calibration by setting bit

the status byte, and by switching off the associated RUN LED. Calibration can be disabled by the controller

via control byte

if necessary. If calibration is disabled over a prolonged period, the terminal

carries out a forced calibration, in order to compensate any voltage drifts that may be caused by changes in

temperature. The forced calibration interval is specified via register

as a multiple of the calibration

interval. If a further calibration between two cycles is required, this can be started manually by setting bit

. The terminal then acts as if it had triggered a calibration itself.

Fluctuating measurement signals disturbing the self‑calibration

The terminal checks by a stabilization test while in calibration state whether the input signal is sta-

ble. Large variations of measurement signals prevent a completion of the self‑calibration; the termi-

nal remains in Error=1 and overload/underload=1, see sections

"Basic function principles/ Calibra-

"Access from the user program/ Status byte 1 (for process data mode)" [

If such a signal will be expected on a system plant, you can optionally:

‑ lock the self‑calibration within the process via Control‑Bit

present and the self‑calibration passes.

‑ disabling the stabilization test process via bit

‑ disabling the indication of the stabilization error by bit

.

‑ increase the tolerance window of the stabilization control by register

The functionality of the calibration including all features invariably refers to both channels simultaneously!

The channels cannot be calibrated individually. For this reason, the registers

and

are only implemented once for both channels.