– 186 –

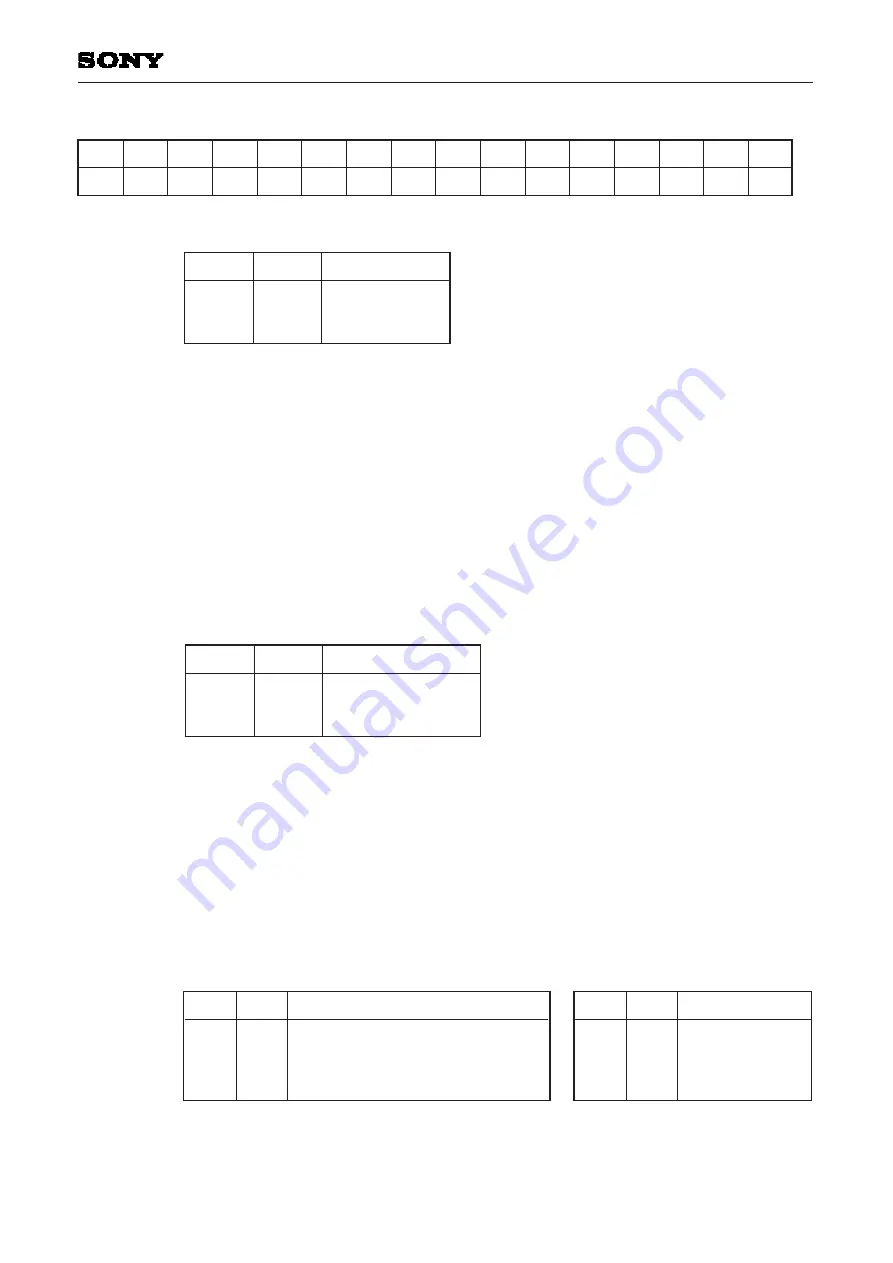

CXD3068Q

$3C (preset: $3C 00 80)

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

COSS COTS CETZ CETF COT2 COT1 MOT2

0

BTS1 BTS0 MRC1 MRC0

0

0

0

0

COSS, COTS: This selects the TZC signal used when generating the COUT signal.

Preset = HPTZC.

STZC is the TZC generated by sampling the TE signal at 700kHz. (when MCK = 128Fs)

DTZC is the delayed phase STZC. (The delay time can be selected by D14 of $36.)

HPTZC is the fast phase TZC passed through a HPF with a cut-off frequency of 1kHz.

See § 5-13.

CETZ:

The input from the TE pin normally enters the TRK filter and is used to generate the TZC

signal. However, the input from the CE pin can also be used. This function is for the center

error servo.

When 0, the TZC signal is generated by using the signal input to the TE pin.

When 1, the TZC signal is generated by using the signal input to the CE pin.

CETF:

When 0, the signal input to the TE pin is input to the TRK servo filter.

When 1, the signal input to the CE pin is input to the TRK servo filter.

These commands output the TZC signal.

COT2, COT1: This outputs the TZC signal from the COUT pin.

COSS

1

0

0

—

0

1

STZC

HPTZC

DTZC

COTS

TZC

∗

: preset, —: don't care

∗

BTS1

0

0

1

1

0

1

0

1

1

2

4

8

BTS0

Number of count-up steps per cycle

MRC1

0

0

1

1

0

1

0

1

5.669

∗

11.338

22.675

45.351

MRC0

Setting time [µs]

∗

: preset (when MCK = 128Fs)

∗

MOT2:

The STZC signal is output from the MIRR pin by setting MOT2 to 1.

These commands set the MIRR signal generation circuit.

BTS1, BTS0:

This sets the count-up speed for the bottom hold value of the MIRR generation circuit.

The time per step is approximately 708ns (when MCK = 128Fs). The preset value is BTS1 = 1,

BTS0 = 0 like the CXD2586R. This is valid only when BTF of $3B is 0.

MRC1, MRC0: This sets the minimum pulse width for masking the MIRR signal of the MIRR generation circuit.

As noted in § 5-9, the MIRR signal is generated by comparing the waveform obtained by

subtracting the bottom hold value from the peak hold value with the MIRR comparator level.

Strictly speaking, however, for MIRR to become high, these levels must be compared

continuously for a certain time. This sets that time.

The preset value is MRC1 = 0, MRC0 = 0 like the CXD2586R.

COT2

1

0

0

—

1

0

STZC

HPTZC

COUT

COT1

COUT pin output

∗

: preset, —: don't care

∗

Содержание PV420S

Страница 1: ...SERVICE MANUAL PV420S WWW BBK RU ...

Страница 72: ... 69 CXD3068Q Block Diagram ...

Страница 73: ... 70 CXD3068Q Pin Configuration ...

Страница 122: ... 119 CXD3068Q Timing Chart 1 3 ...

Страница 123: ... 120 CXD3068Q Timing Chart 1 4 ...

Страница 124: ... 121 CXD3068Q Timing Chart 1 5 ...

Страница 127: ... 124 CXD3068Q Timing Chart 1 16 CAV W mode EPWM 1 LPWR 0 Timing Chart 1 17 CAV W mode EPWM LPWR 1 ...

Страница 129: ... 126 CXD3068Q Timing Chart 2 1 ...

Страница 130: ... 127 CXD3068Q Block Diagram 2 2 ...

Страница 131: ... 128 CXD3068Q Timing Chart 2 3 ...

Страница 134: ... 131 CXD3068Q Timing Chart 2 6 ...

Страница 137: ... 134 CXD3068Q Fig 3 1 Disc Stop to Regular Playback in CLV W Mode CLV W Mode Fig 3 2 CLV W Mode Flow Chart ...

Страница 138: ... 135 CXD3068Q VCO C Mode Fig 3 3 Access Flow Chart Using VCO Control ...

Страница 140: ... 137 CXD3068Q Block Diagram 4 1 ...

Страница 143: ... 140 CXD3068Q Timing Chart 4 4 ...

Страница 147: ... 144 CXD3068Q Fig 4 6 a Auto Focus Flow Chart Fig 4 6 b Auto Focus Timing Chart ...

Страница 148: ... 145 CXD3068Q Fig 4 7 a 1 Track Jump Flow Chart Fig 4 7 b 1 Track Jump Timing Chart ...

Страница 149: ... 146 CXD3068Q Fig 4 8 a 10 Track Jump Flow Chart Fig 4 8 b 10 Track Jump Timing Chart ...

Страница 150: ... 147 CXD3068Q Fig 4 9 a 2N Track Jump Flow Chart Fig 4 9 b 2N Track Jump Timing Chart ...

Страница 151: ... 148 CXD3068Q Fig 4 10 a Fine Search Flow Chart Fig 4 10 b Fine Search Timing Chart ...

Страница 152: ... 149 CXD3068Q Fig 4 11 a M Track Move Flow Chart Fig 4 11 b M Track Move Timing Chart ...

Страница 157: ... 154 CXD3068Q Fig 4 15 CD TEXT Data Timing Chart ...

Страница 162: ... 159 CXD3068Q Fig 5 3a Fig 5 3b ...

Страница 176: ... 173 CXD3068Q Fig 5 26a Servo HighBooster Characteristics FCS TRK MCK 128Fs HBST1 0 HBST1 1 HBST0 0 HBST1 1 HBST0 1 ...

Страница 177: ... 174 CXD3068Q Fig 5 26b Servo LowBooster1 Characteristics FCS TRK MCK 128Fs LB1S1 0 LB1S1 1 LB1S0 0 LB1S1 1 LB1S0 1 ...

Страница 178: ... 175 CXD3068Q Fig 5 26c Servo LowBooster2 Characteristics FCS TRK MCK 128Fs LB2S1 0 LB2S1 1 LB2S0 0 LB2S1 1 LB2S0 1 ...

Страница 196: ... 193 CXD3068Q Description of Data Readout ...

Страница 200: ... 197 CXD3068Q ...

Страница 201: ... 198 CXD3068Q ...

Страница 202: ... 199 CXD3068Q ...

Страница 203: ... 200 CXD3068Q SLD Servo fs 345Hz Note Set the MSB bit of the K02 and K04 coefficients to 0 HPTZC Auto Gain fs 88 2kHz ...

Страница 207: ... 204 CXD3068Q Package Outline Unit mm ...

Страница 208: ...This data sheet has been made from recycled paper to help protect the environment 205 ...