71

ATmega161(L)

1228B–09/01

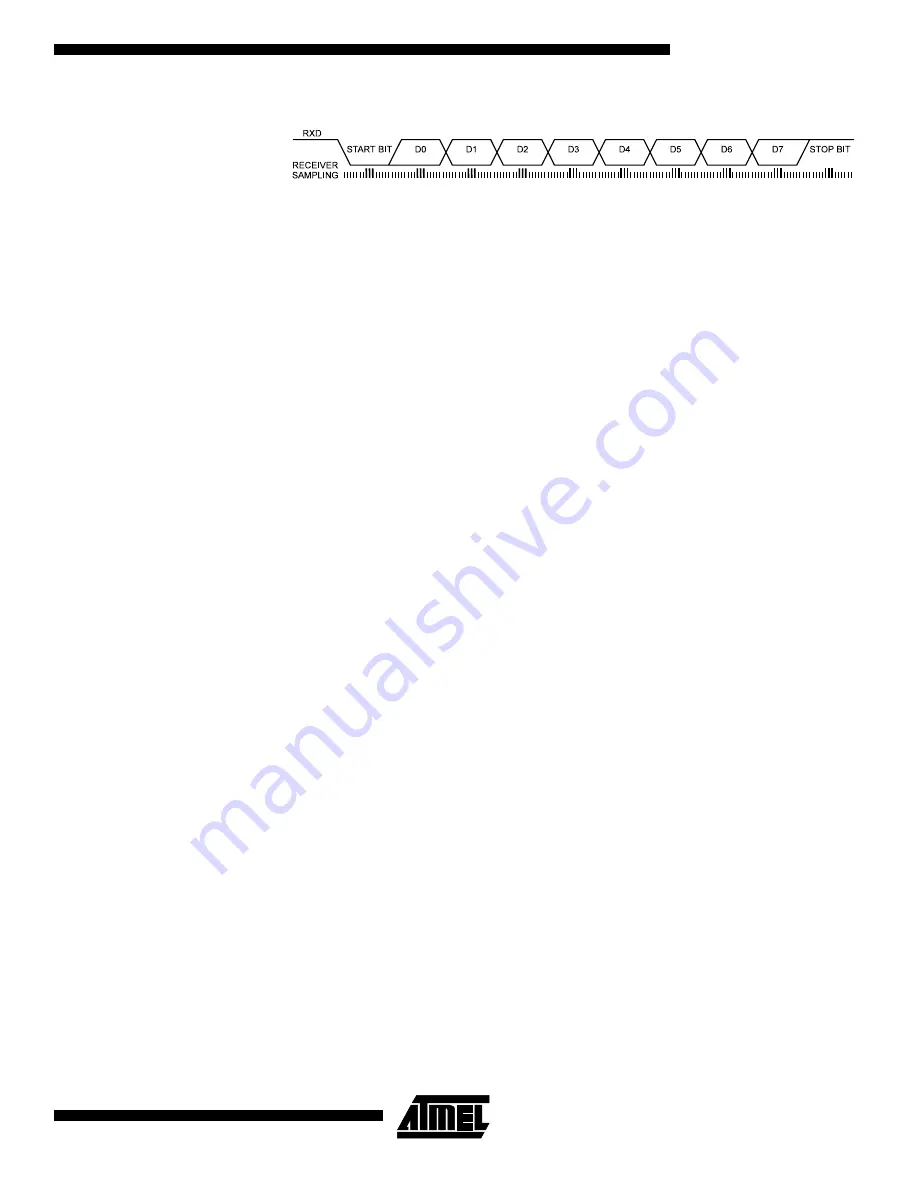

Figure 47.

Sampling Received Data

Note:

1. This figure is not valid when the UART speed is doubled. See

for a detailed description.

When the stop bit enters the receiver, the majority of the three samples must be one to

accept the stop bit. If two or more samples are logical “0”s, the Framing Error (FEn) flag

in the UART Control and Status Register (UCSRnA) is set. Before reading the UDRn

register, the user should always check the FEn bit to detect framing errors.

Whether or not a valid stop bit is detected at the end of a character reception cycle, the

data is transferred to UDRn and the RXCn flag in UCSRnA is set. UDRn is in fact two

physically separate registers, one for transmitted data and one for received data. When

UDRn is read, the Receive Data register is accessed, and when UDRn is written, the

Transmit Data register is accessed. If 9-bit data word is selected (the CHR9n bit in the

UART Control and Status Register [UCSRnB] is set), the RXB8n bit in UCSRnB is

loaded with bit 9 in the Transmit shift register when data is transferred to UDRn.

If, after having received a character, the UDRn register has not been read since the last

receive, the OverRun (ORn) flag in UCSRnB is set. This means that the last data byte

shifted into the shift register could not be transferred to UDRn and has been lost. The

ORn bit is buffered and is updated when the valid data byte in UDRn is read. Thus, the

user should always check the ORn bit after reading the UDRn register in order to detect

any overruns if the baud rate is high or CPU load is high.

When the RXEN bit in the UCSRnB register is cleared (zero), the receiver is disabled.

This means that the PD0 pin can be used as a general I/O pin. When RXEN is set, the

UART receiver will be connected to PD0 (UART0) or PB2 (UART1), which is forced to

be an input pin regardless of the setting of the DDD0 in DDRD (UART0) or DDB2 bit in

DDRB (UART1). When PD0 (UART0) or PB2 (UART1) is forced to input by the UART,

the PORTD0 (UART0) or PORTB2 (UART1) bit can still be used to control the pull-up

resistor on the pin.

Note that PB2 (UART1) also is used as one of the input pins to the Analog Comparator.

It is therefore not recommended to use UART1 if the Analog Comparator also is used in

the application at the same time.

When the CHR9n bit in the UCSRnB register is set, transmitted and received characters

are nine bits long plus start and stop bits. The ninth data bit to be transmitted is the

TXB8n bit in UCSRnB register. This bit must be set to the wanted value before a trans-

mission is initiated by writing to the UDRn register. The ninth data bit received is the

RXB8n bit in the UCSRnB register.

Multi-processor

Communication Mode

The Multi-processor Communication Mode enables several slave MCUs to receive data

from a master MCU. This is done by first decoding an address byte to find out which

MCU has been addressed. If a particular slave MCU has been addressed, it will receive

the following data bytes as normal, while the other slave MCUs will ignore the data bytes

until another address byte is received.

For an MCU to act as a master MCU, it should enter 9-bit transmission mode (CHR9n in

UCSRnB set). The ninth bit must be one to indicate that an address byte is being trans-

mitted, and zero to indicate that a data byte is being transmitted.