UG-076

Evaluation Board User Guide

Rev. A | Page 8 of 16

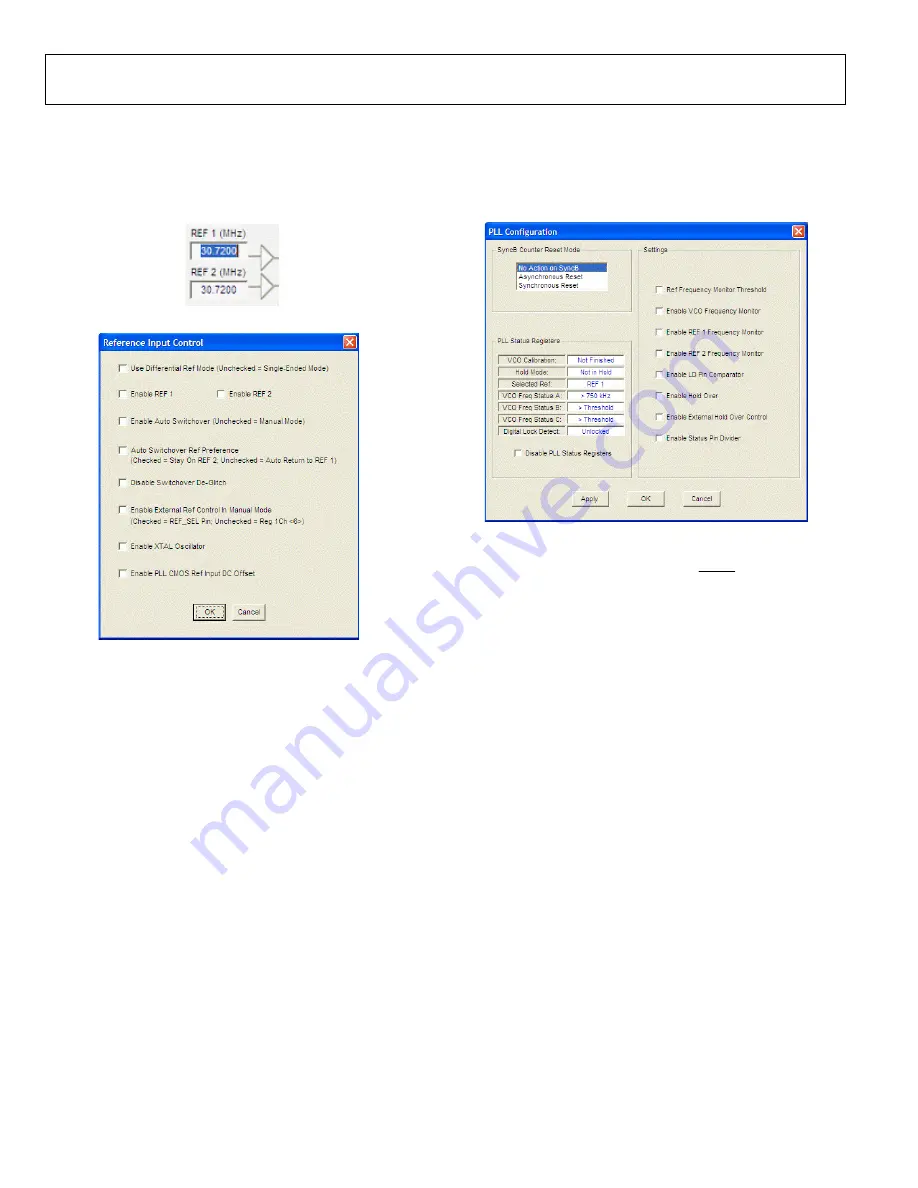

PLL REFERENCE INPUT WINDOW

The

Reference Input Control

window is shown in Figure 10

and is accessed by clicking either of the triangular buffer

symbols immediately to the right of the

REF 1 (MHz)

and

REF 2 (MHz)

input reference frequency boxes (see Figure 9).

0

874

6-

024

Figure 9. Buffer Symbol

0

87

46-

0

06

Figure 10.

Reference Input Control

Window

This window is used to enable the PLL reference inputs, which

are powered down by default.

Select

Enable REF 1

,

Enable REF 2

, or both to enable the

appropriate reference input and click

OK

when finished. If a

differential input is used, select the

Use Differential Ref Mode

(Unchecked = Single-Ended Mode)

check box. Note that this

mode must not be used simultaneously with

Enable REF 1

or

Enable REF 2

.

The remaining six check boxes control the reference switchover

modes. If

Disable Switchover De-Glitch

is activated, the

maintains the phase relationship between the active input and

PLL output during a reference switchover. Otherwise, the

minimizes the phase disturbance at the output

during a reference switchover.

The user must check

Enable XTAL Oscillator

if intending to

connect a crystal to the reference input.

Enable PLL CMOS Ref Input DC Offset

forces the dc bias

point of the single-ended reference input to be different from

the switching point, and is useful for preventing an ac-coupled

input from chattering when the reference input is lost.

PLL CONFIGURATION WINDOW

The

PLL Configuration

window shown in Figure 11 is opened

by clicking the

Config PLL

button on the main screen. The

window has three sections:

SyncB Counter Reset Mode

,

PLL

Status Registers

, and

Settings

.

087

46

-00

7

Figure 11.

PLL Configuration

Window

The

SyncB Counter Reset Mode

section indicates whether the

R, A, and B counters are reset when the SYNC pin is activated,

and controls Register 0x019, Bits[7:6]. See the

data

sheet for more details.

The

PLL Status Registers

section allows the user to see the

current value of the readonly PLL status register, Address 0x01F.

This function is useful for ensuring that the

VCO has

finished VCO calibration, and that the PLL is locked.

The

Settings

section controls the various PLL settings such

as holdover. The

data sheet describes these functions

in detail.

REFMON, STATUS, AND LD BUTTONS

These three blue buttons (

REFMON

,

STATUS

, and

LD

) allow

the user to select which signals appear at the REFMON,

STATUS, and LD pins at Connector P1. Connector P1 is located

in the center of the evaluation board. The pins in the left

column of Connector P1 are ground pins, and the ones in the

right column are signal pins.

There are many useful diagnostic signals available at these

pins. The R divider output is particularly useful. In the example

used in the Quick Start Guide to the AD9520 PLL section, the

80 kHz signal is visible on the STATUS pin to ensure that the

reference inputs and R divider are working properly.

Dynamic signals (such as the R divider output) are primarily

intended for diagnostics. These diagnostic signals may adversely

affect PLL performance in critical applications if left on in

normal operation.