ADM-PCIE-8V3 User Manual

3.3 PCI Express

The ADM-PCIE-8V3 is capable of PCIe Gen 1/2/3 with 1/2/4/8/16 lanes (where 16-lanes requires a two

bifurcated 8-lane interfaces). The FPGA drives these lanes directly using the Integrated PCI Express block from

Xilinx. Negotiation of PCIe link speed and number of lanes used is generally automatic and does not require user

intervention.

PCI Express reset (PERST#) connected to the FPGA at both pins AJ31 and AP33.

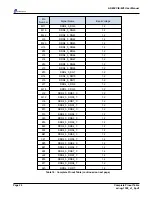

The other pin assignments for the high speed lanes are provided in the pinout attached to the

Complete Pinout

Table

Note:

Different motherboards/backplanes will benefit from different RX equalization schemes within the PCIe IP core

provided by Xilinx. Alpha Data recommends using the following setting if a user experiences link errors or

training issues with their system: within the IP core generator, change the mode to "Advanced" and open the

"GT Settings" tab, change the "form factor driven insertion loss adjustment" from "Add-in Card" to

"Chip-to-Chip" (See Xilinx PG239 for more details).

3.4 DDR4 SDRAM

Two banks of DDR4 SDRAM memory are soldered down to the board. While the factory default is 8GB/per bank,

16GB/bank is also supported through a built variant. Please see

Order Code

for all order options. The memory

interface is 72-bit wide data (64 data + 8 ECC). Maximum signaling rate is 2400 MT/s for 16GB total and

1688MT/s with 32GB total.

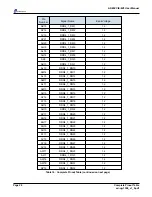

Memory solutions are available from the Xilinx Memory Interface Generator (MIG) tool. An example memory

excersizer project is included in the ADM-PCIE-8V3 SDK. All constraint information is included in

Complete

Pinout Table

. Alpha Data has also provided a custom csv timing file for use with Xilinx MIG. This can be

downloaded from the ADM-PCIE-8V3 product page.

8Gb components used (standard) are Micron MT40A1G8PM-083E

16Gb components used (build variant) are Micron MT40A2G8PM-093E

Page 11

Functional Description

ad-ug-1308_v1_9.pdf

Содержание ADM-PCIE-8V3

Страница 1: ...ADM PCIE 8V3 User Manual Document Revision 1 9 28th June 2017...

Страница 8: ...ADM PCIE 8V3 User Manual Figure 3 Optional Blower Page 4 PCB Information ad ug 1308_v1_9 pdf...

Страница 24: ...ADM PCIE 8V3 User Manual Page Intentionally left blank Page 20 Functional Description ad ug 1308_v1_9 pdf...