SERIES IP236 INDUSTRIAL I/O PACK FIFO BUFFERED 16 BIT ANALOG OUTPUT MODULE

___________________________________________________________________________________________

- 3 -

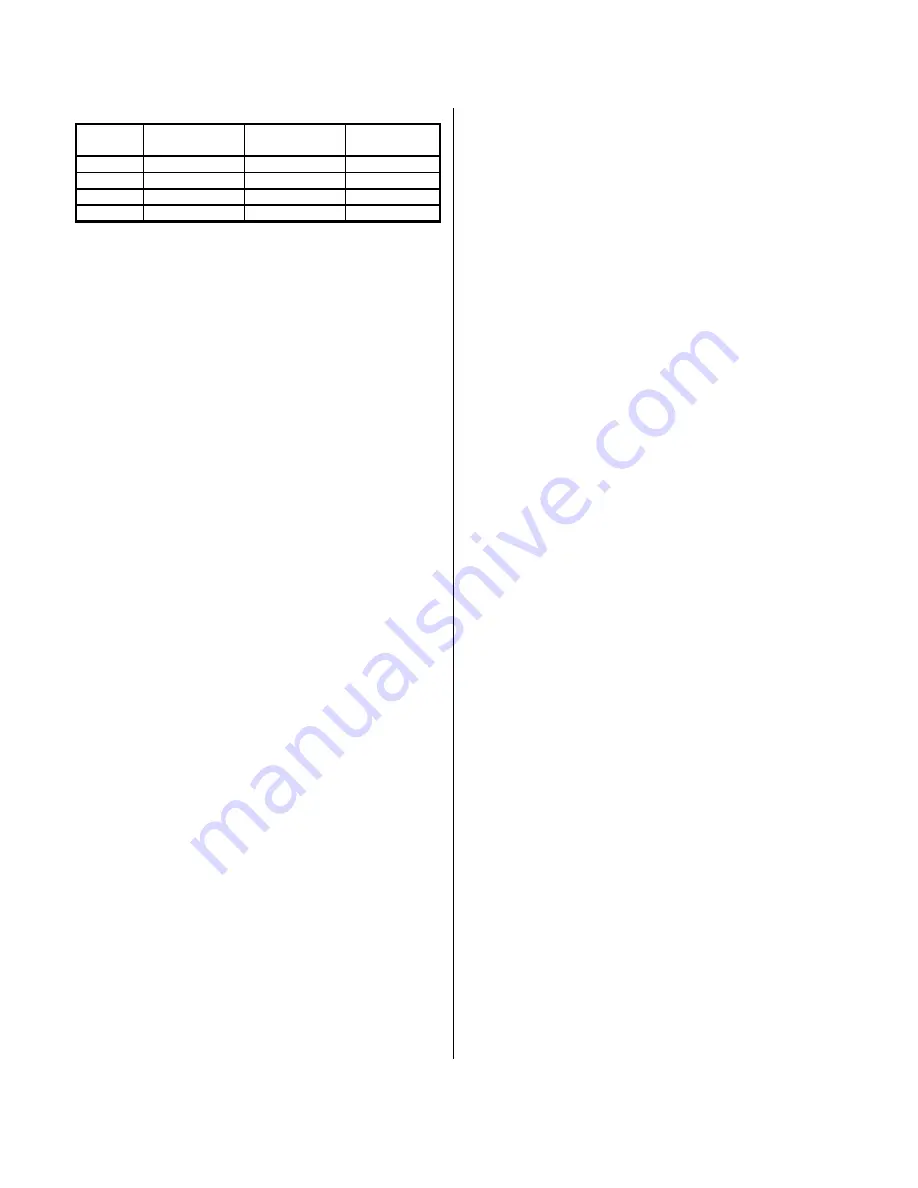

Model

Analog Output

Channels

FIFO Buffer Per

Channel

Temperature

Range

IP236-4

4

Yes

0 to +70

°

C

IP236-4E

4

Yes

-40

°

C to +85

°

C

IP236-8

8

Yes

0 to +70

°

C

IP236-8E

8

Yes

-40

°

C to +85

°

C

KEY IP236 FEATURES

•

DAC 16-Bit Resolution

- 16-bit monolithic DAC with bipolar

voltage output ranges of

±

10V,

±

5V, and an unipolar output

range of 0 to 10V. The IP236-8 will have eight

independently controlled DACs present on the board while

the IP236-4 will have four.

•

10

µ

µµ

µ

sec Conversion Time

- A maximum recommended

conversion rate of 100KHz, for specified accuracy, is

supported. The absolute maximum conversion rate of

150KHz is also supported.

•

128-Sample FIFO Buffers -

Each DAC channel provides

128-sample data buffering to reduce CPU interactions and

interrupts. This allows the external processor to handle

more tasks within a given time.

•

Continuous Conversion Mode -

Each of the channel’s

FIFOs can be filled/loaded with new data without stopping

output waveform generation.

•

Single Step Mode

- On each new software or external

trigger, each output channel can be independently updated

with a new DAC value read from their corresponding FIFO

buffer.

•

Interrupt Support -

Individually controlled FIFO almost

empty interrupts may be generated. Unique interrupt

thresholds can be assigned to each channel. On a FIFO

almost empty interrupt, the interrupt service routine could fill

the FIFO with new data while output waveform generation

continues. Thus, allowing continuous conversions.

•

User Programmable Interval Timer

- Each channel has a

user programmable interval timer provided to control the

delay between conversions. Each channel is independently

converted at the rate set by its corresponding interval timer.

This feature supports a minimum interval of 6.7

µ

sec and a

maximum interval of 2.09 seconds.

•

FIFO Full and Almost Empty Flags-

Individual FIFO Full

and Almost Empty flag bits are available to implement

software polling schemes for FIFO buffer data control.

•

External Trigger Scan Mode

- Each channel has an

external trigger which is assigned to a field I/O line. Thus,

all channels can independently initiate a new conversion

with each external trigger via its dedicated external trigger

pin. This mode allows synchronization of conversions with

external events that are often asynchronous.

•

External Trigger Output

- The external trigger may be

configured as an output signal to provide a means to

synchronize other channels or IP236 devices to a single

IP236 channel or module.

•

Reliable Software Calibration

- Calibration coefficients

stored on-board provide the means for accurate software

calibration for both gain and offset correction for each of the

channels of the module.

•

Reset is Failsafe For Bipolar Output Ranges -

When the

module’s jumpers are set for bipolar operation, the analog

outputs are reset to 0 volts upon power up or receipt of a

software or hardware reset. This eliminates the problem of

applying random output voltages to actuators during power

on sequences.

•

Hardware Jumper Setting For Selection of DAC Ranges

-

Both bipolar (

±

5V,

±

10V) and unipolar (0 to 10V) ranges are

available. The ranges can be selected on a per channel

basis.

•

High Density

- Provides programmable control of eight

analog voltage output channels. Four units mounted on a

VMEbus or ISAbus carrier board provide 32 DAC channels

in a single system slot. On the PCIbus carrier, up to five

units may be mounted to provide up to 40 DAC channels per

PCI system slot.

•

Extended Temperature Performance Option -

Models

IP236-8E and IP236-4E units support operation from -40

°

C

to +85

°

C.

INDUSTRIAL I/O PACK INTERFACE FEATURES

•

High density -

Single-size, industry standard, IP module

footprint. Four/five units mounted on a carrier board provide

up to 32/40 serial ports in a single system slot.

•

Local ID

- Each IP module has its own 8-bit ID information

which is accessed via data transfers in the "ID Read" space.

•

16-bit and 8-bit I/O

- Port register Read/Write is performed

through data transfer cycles in the IP module I/O space.

•

High Speed

- Access times for all data transfer cycles are

described in terms of "wait" states - 0 wait state is required

for reading and writing all control registers and ID values.

Interrupt select cycles also require 0 wait states for reading

the interrupt vector. Two wait states are typically required to

write the channel data FIFO ports (see the Specifications

section for detailed information).

SIGNAL INTERFACE PRODUCTS

(See Appendix for more information on compatible products)

This IP module will mate directly to any industry standard IP

carrier board (including Acromag’s AVME9630/9660 3U/6U

VMEbus carrier boards). Additionally, PC/AT carrier boards are

also supported (see the Acromag Model APC8620 PCIbus carrier

board). A wide range of other Acromag IP modules are available

to serve your signal conditioning and interface needs.

The cables and termination panels, described in the following

paragraphs, are also available. For optimum performance with

the 16-bit IP236 analog output modules, use of the shortest

possible length of shielded output cable is recommended. Since

all connections to field signals are made through the carrier board

which passes them to the individual IP modules, you should

consult the documentation of your carrier board to ensure

compatibility with the following interface products.

Cables:

Model 5025-551-X (Shielded Cable), or Model 5025-550-X

(Non-Shielded Cable): A Flat 50-pin cable with female

connectors at both ends for connecting AVME9630/9660,

APC8610, or APC8620 carrier boards, to Model 5025-552

termination panels. The unshielded cable is recommended

for digital I/O, while the shielded cable is recommended for

optimum performance with precision analog I/O applications.

The “-X” suffix of the model number is used to indicate the

length in feet.