MC96FM204/FM214

68

April 7, 2016 Ver. 1.8

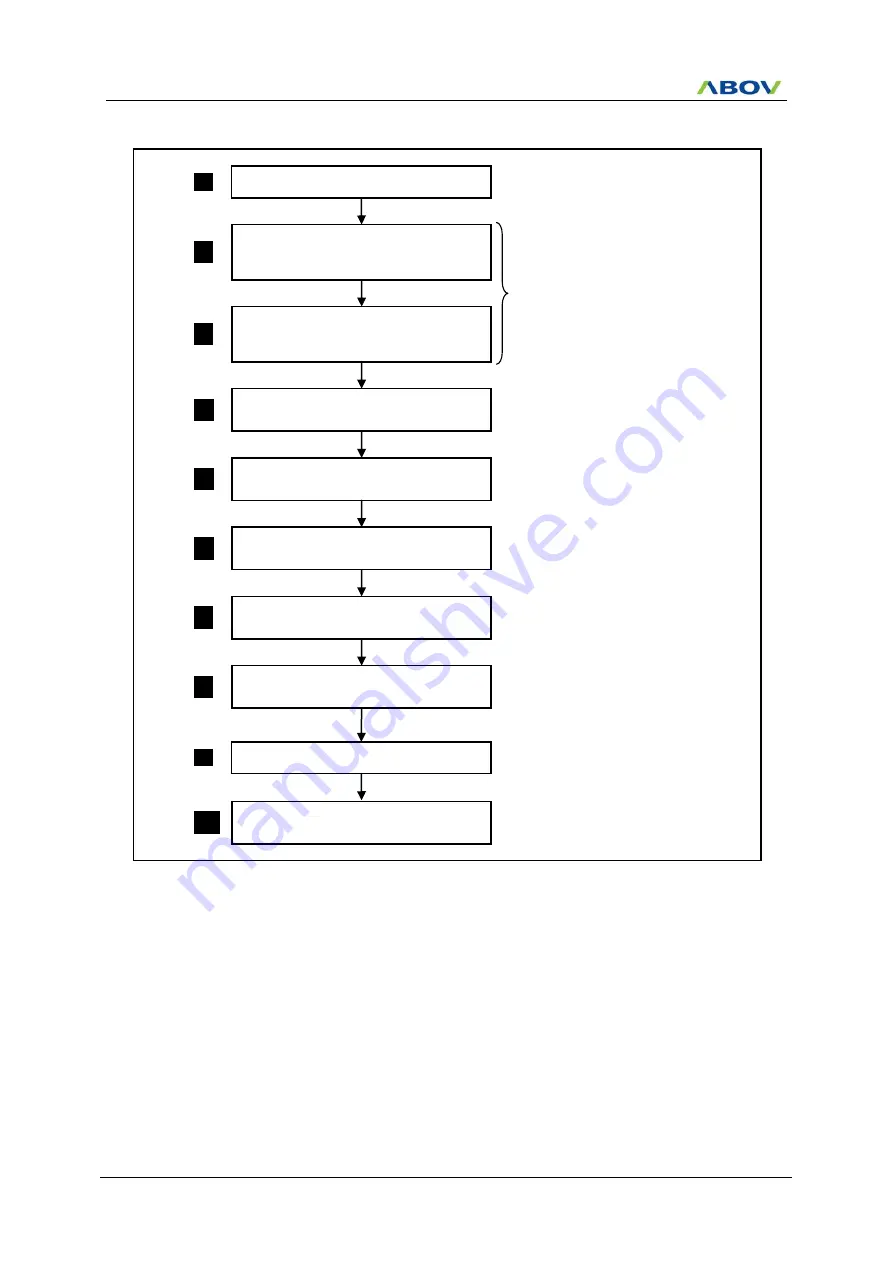

Figure 10.3 Interrupt Vector Address Table

Saves PC value in order to continue

process again after executing ISR

IE.EA Flag

0

1

Program Counter low Byte

SP

SP + 1

M(SP)

(PCL)

2

Program Counter high Byte

SP

SP + 1

M(SP)

(PCH)

3

Interrupt Vector Address occurrence

(Interrupt Vector Address)

4

ISR(Interrupt Service Routine) move,

execute

5

Return from ISR

RETI

6

Program Counter high Byte recovery

(PCH)

(SP-1)

7

Main Program execution

10

Program Counter low Byte recovery

(PCL)

(SP-1)

8

IE.EA Flag

1

9

Содержание MC96FM204

Страница 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Страница 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Страница 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Страница 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...