TRIPL1

BLOCK

AND

L1TRIP

t

tEvolvingFault

t

tTripMin

L2TRIP

L3TRIP

P3PTR

OR

OR

OR

AND

TRIP

IEC17000065-2-en.vsdx

IEC17000065 V2 EN-US

Figure 218:

Simplified additional logic per phase, Program = 1ph/3ph or

1ph/2ph/3ph

IEC17000066=1=en=Original.vsdx

TRL1

t

3ms

BLKLKOUT

OR

OR

TRIPL1

AND

TRIPL3

TRIPL2

TRIPALL

TRL2

TRL3

-LOOP

AND

-LOOP

OR

AND

OR

OR

OR

OR

AND

AND

OR

AND

AND

OR

t

10 ms

t

5 ms

TR3P

AND

OR

SETLKOUT

RSTLKOUT

AND

OR

-LOOP

-LOOP

AND

AND

TR1P

TR2P

CLKLKOUT

AutoLock

TripLockout

TRIP

To ensure that the

fault is single phase

To ensure that the

fault is two phase

IEC17000066 V1 EN-US

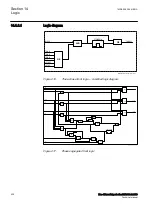

Figure 219:

Final tripping circuits

1MRK 505 394-UEN A

Section 14

Logic

Line differential protection RED650 2.2 IEC

439

Technical manual

Содержание RED650

Страница 1: ...RELION 650 SERIES Line differential protection RED650 Version 2 2 Technical manual...

Страница 2: ......

Страница 36: ...30...

Страница 46: ...40...

Страница 232: ...226...

Страница 272: ...266...

Страница 288: ...282...

Страница 306: ...300...

Страница 406: ...400...

Страница 436: ...430...

Страница 502: ...496...

Страница 614: ...608...

Страница 628: ...622...

Страница 644: ...638...

Страница 760: ...754...

Страница 778: ...772...

Страница 814: ...808...

Страница 870: ...864...

Страница 874: ...868...

Страница 924: ...918...

Страница 925: ...919...