AD484 user manual

V1.2

AD484 User manual

February 2007

www.4dsp.com

- 17 -

4 Power requirements

The power is supplied to the AD484 via the PMC and/or XMC connectors. Several DC-DC

converters generate the appropriate voltage rails for the different devices and interfaces

present on board.

The AD484 power consumption depends mainly on the FPGA devices work load. By using

high efficiency power converters, all care has been taken to ensure that power consumption

will remain as low as possible for any given algorithm.

After power up the AD484 typically consumes 5W of power. For precise power

measurements it is recommended to use the Xilinx power estimation tools for both FPGA A

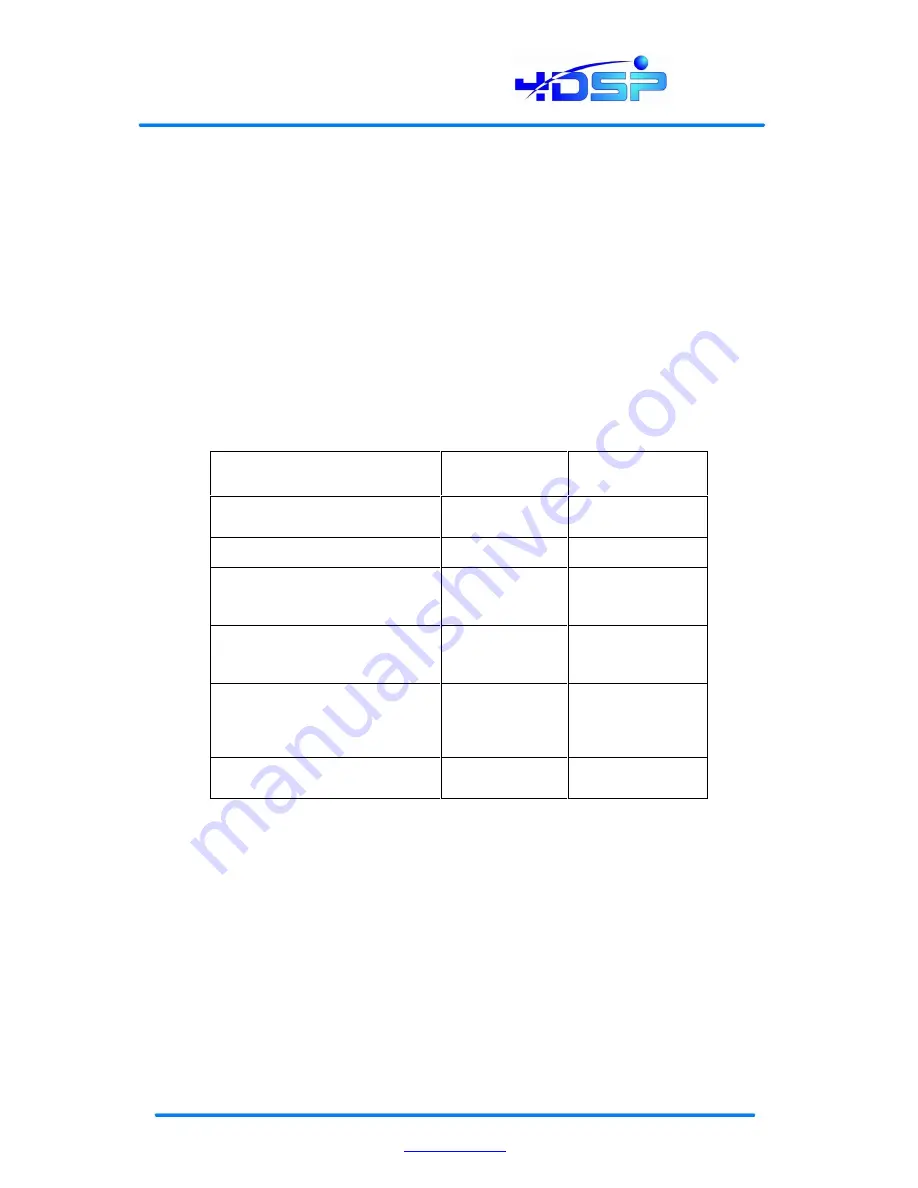

and B. The maximum current rating given in the table below is the maximum current that can

be drawn from each voltage rail in the case resources are used to their maximum level.

Device/Interface

Voltage

Maximum

current rating

DCI

and

memory

reference

voltage

0.9V

5 A

Virtex-4 device A & B core

1.2V

12A

QDR2, DDR2 SDRAM core and

I/O banks, Virtex-4 devices I/O

banks

1.8V

10A

Virtex-4

device

B

I/O

bank

connected to the front panel

daughter card

1.8V/2.5/3.3V

1.5A

Virtex-4

device

A

I/O

bank

connected to the PCI bus, Flash,

CPLD, front Panel I/O daughter

card, A/D circuitry

3.3V

4A

MGT power supply

1.2V, 1.5V, 2.5V

1.7A, 0.5A, 0.01A

respectively

Table 7 : Power supply