AD484 user manual

V1.2

AD484 User manual

February 2007

www.4dsp.com

- 12 -

Figure 5: CPLD LED locations

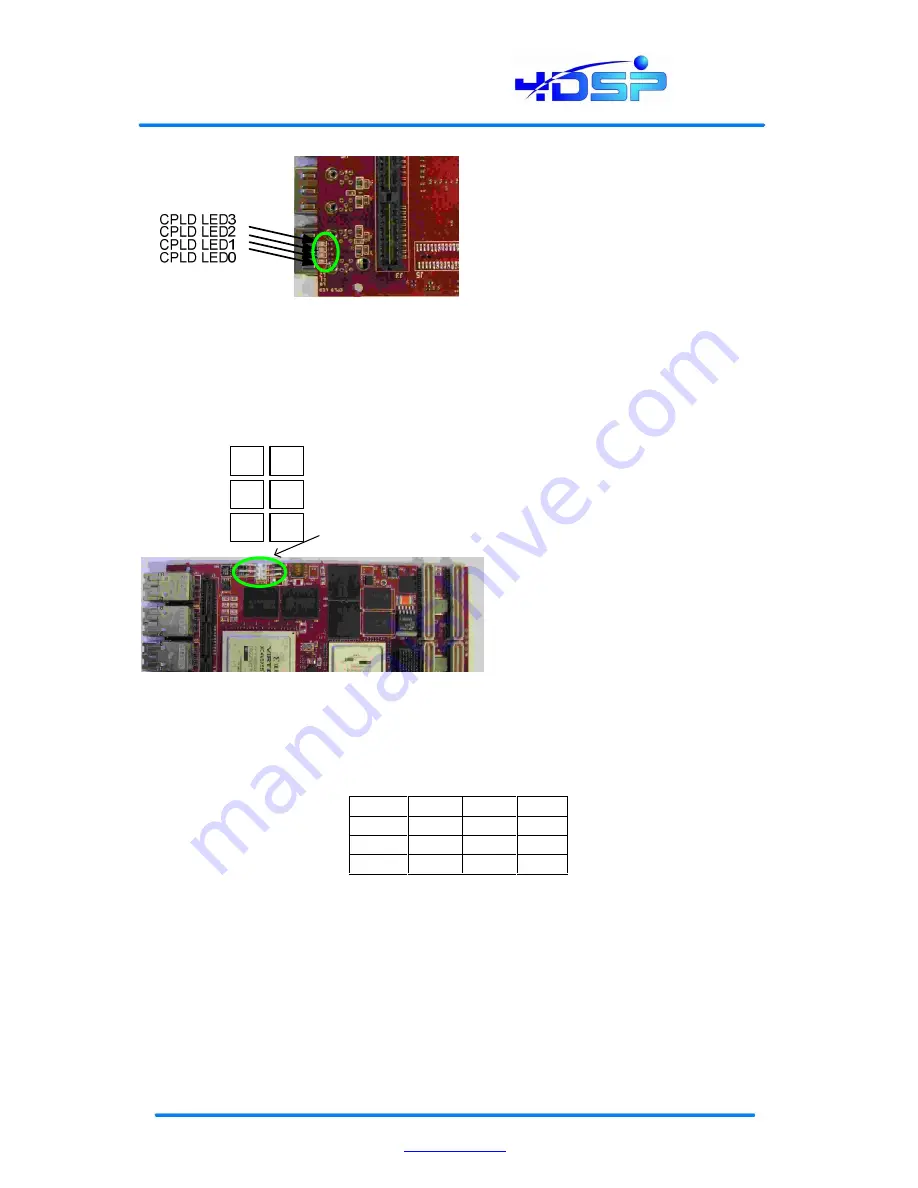

3.2.3 JTAG

A JTAG connector is available on the AD484 for configuration purposes. The JTAG can also

be used to debug the FPGA design with the Xilinx Chipscope.

The JTAG connector is located on side 1 of the PCB in front (see Figure 6).

-7$*FRQQHFWRU

YFF

JQG

WFN

WPV

WGL

WGR

Figure 6: JTAG connector (J6) location

The JTAG connector pinout is as follows:

Pin #

Signal Signal

Pin #

1

1.8V

TMS

4

2

GND

TDI

5

3

TCK

TDO

6

Table 5 : JTAG pin assignment