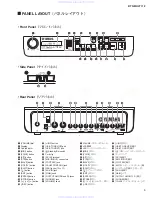

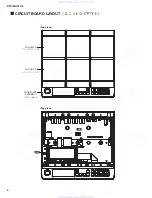

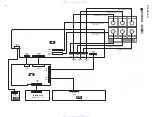

DTX-MULTI 12

14

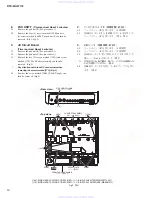

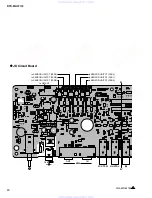

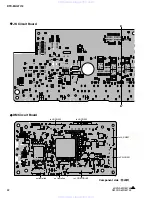

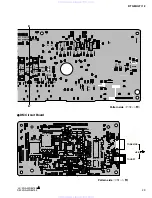

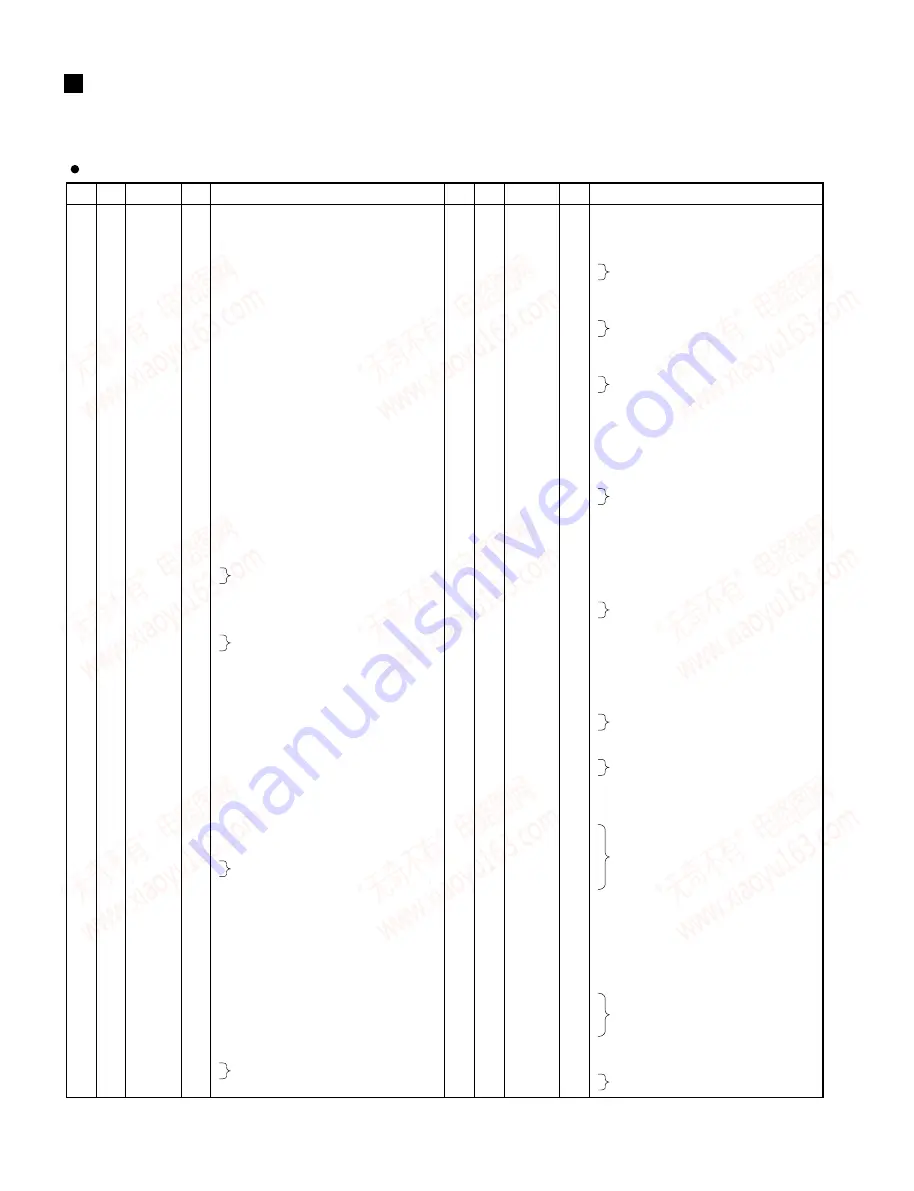

LSI PIN DESCRIPTION

(

LSI

端子機能表)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

C1

C2

C3

C4

C5

C6

C7

C8

C9

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

VSS

AN2

AN1

VSS

RxD1

SCK1

UCLK

VSS

FUNC_DM

VSS

HOST_DM

POWER_ENB

XTAL

EXTAL

VSS

CS7N/PJ6

TRSTN

TDI

TCK

VCCQ

MD15

VSS

AN3

AN0

VSS

TxD1

TxD0

VSS

FUNC_DP

VSS

HOST_DP

SCL

VSS

VSS

CS4N/PJ3

TIOC0A/PJ7

TESTN

TMS

VCCQ

VCCQ

MD13

MD14

VSS

VREFADC

VSSADC

VSS

RxD0

VSS

VBUS

RESN

VCCQ

PULLUP_ENB

VCCQ

UCTL

EICN

CS1N/PJ0

CS3N/PJ2

CS6N/PJ5

ASEBRKAKN

VCCQ

VCCQ

VSSPLL

-

I

I

-

I

I

I

-

I/O

-

I/O

O

O

I

-

O

I

I

I

-

I/O

-

I

I

-

O

O

-

I/O

-

I/O

I/O

-

-

O

O

I

I

-

-

I/O

I/O

-

-

-

-

I

-

I

-

I

-

-

-

I

-

O

-

I

O

O

O

O

I/O

-

-

-

Ground

ADC analog input 2

ADC analog input 1

Ground

Serial input 1

External sync. clock input 1

USB external clock input (48 MHz)

Ground

USB function data -

Ground

USB host data -

USB voltage enable

Crystal oscillator output

Crystal oscillator input (16.9344 MHz)

Ground

SH2A-CPU chip select 7

JTAG test reset input

JTAG test data input

JTAG test clock input

Power 3.3 V

Wave memory data bus 15

Ground

ADC analog input 3

ADC analog input 0

Ground

Serial output 1

Serial output 0

Ground

USB function data +

Ground

USB host data +

E bus (I2C) clock input/output (5V compatible)

Ground

SH2A-CPU chip select 4

PWM output

Test input

JTAG test mode select input

Power 3.3 V

Wave memory data bus 13

Wave memory data bus 14

Ground

ADC reference power 3.3 V

ADC analog ground

Ground

Serial input 0

Ground

USB cable connection monitor (5V compatible)

Ground

USB overcurrent detection (5V compatible)

E bus (I2C) data input/output (5V compatible)

SH2A-CPU chip select 0

SH2A-CPU chip select 2

SH2A-CPU chip select 5

Debug mode configuration

JTAG test data output

Power 3.3 V

Wave memory data bus 10

Wave memory data bus 11

Wave memory data bus 12

Ground

ADC analog power 3.3 V

Ground

Hardware reset

Power 3.3 V

USB pull-up enable

Power 3.3 V

USB output control

E bus reset output

SH2A-CPU chip select 1

SH2A-CPU chip select 3

SH2A-CPU chip select 6

Emulator break

Power 3.3 V

PLL analog ground

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

D20

E1

E2

E3

E4

E5

E6

E7

E8

E9

E10

E11

E12

E13

E14

E15

E16

E17

E18

E19

E20

F1

F2

F3

F4

F5

F16

F17

F18

F19

F20

G1

G2

G3

G4

G5

G16

G17

G18

G19

G20

H1

H2

H3

H4

H5

H16

H17

H18

H19

H20

J1

J2

J3

J4

J5

J9

J10

J11

J12

J16

J17

J18

J19

J20

K1

K2

K3

K4

K5

K9

K10

K11

K12

K16

K17

K18

K19

K20

VSSPLL

MD6

MD7

MD8

MD9

VDD

VDD

VSS

VCCQ

VSS

VCCQ

VCCQ

VSS

VCCQ

VSS

VDD

VDD

D31/PF7

D30/PF6

D29/PF5

D28/PF4

MD2

MD3

MD4

MD5

VDD

VDD

D27/PF3

D26/PF2

D25/PF1

D24/PF0

MA2

MA1

MD0

MD1

VSS

VSS

D23/PE7

D22/PE6

D21/PE5

D20/PE4

MA6

MA5

MA4

MA3

VCCQ

VCCQ

D19/PE3

D18/PE2

VCCQ

VCCQ

MA10

MA9

MA8

MA7

VSS

VSS

VSS

VSS

VSS

VSS

D17/PE1

D16/PE0

CKOEN

CKIO

MA14

MA13

MA12

MA11

VDD

VSS

VSS

VSS

VSS

VDD

CKE

D15

VSS

VSS

-

I/O

I/O

I/O

I/O

-

-

-

-

-

-

-

-

-

-

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

O

O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

O

O

O

O

-

-

I/O

I/O

-

-

O

O

O

O

-

-

-

-

-

-

I/O

I/O

I

O

O

O

O

O

-

-

-

-

-

-

O

I/O

-

-

PLL analog ground

Wave memory data bus 6

Wave memory data bus 7

Wave memory data bus 8

Wave memory data bus 9

Power 1.2 V

Ground

Power 3.3 V

Ground

Power 3.3 V

Ground

Power 3.3 V

Ground

Power 1.2 V

SH2A-CPU data bus 31

SH2A-CPU data bus 30

SH2A-CPU data bus 29

SH2A-CPU data bus 28

Wave memory data bus 2

Wave memory data bus 3

Wave memory data bus 4

Wave memory data bus 5

Power 1.2 V

SH2A-CPU data bus 27

SH2A-CPU data bus 26

SH2A-CPU data bus 25

SH2A-CPU data bus 24

Wave memory address bus 2

Wave memory address bus 1

Wave memory data bus 0

Wave memory data bus 1

Ground

SH2A-CPU data bus 23

SH2A-CPU data bus 22

SH2A-CPU data bus 21

SH2A-CPU data bus 20

Wave memory address bus 6

Wave memory address bus 5

Wave memory address bus 4

Wave memory address bus 3

Power 3.3 V

SH2A-CPU data bus 19

SH2A-CPU data bus 18

Power 3.3 V

Wave memory address bus 10

Wave memory address bus 9

Wave memory address bus 8

Wave memory address bus 7

Ground

SH2A-CPU data bus 17

SH2A-CPU data bus 16

Clock output control for SDRAM

Clock output for SDRAM

Wave memory address bus 14

Wave memory address bus 13

Wave memory address bus 12

Wave memory address bus 11

Power 1.2 V

Ground

Power 1.2 V

Clock enable for SDRAM

SH2A-CPU data bus 15

Ground

R8A02032BG

(X8810A00)

CPU

(SWX02)

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299