Virtex-6 FPGA System Monitor

59

UG370 (v1.1) June 14, 2010

Application Guidelines

EDK Support for System Monitor

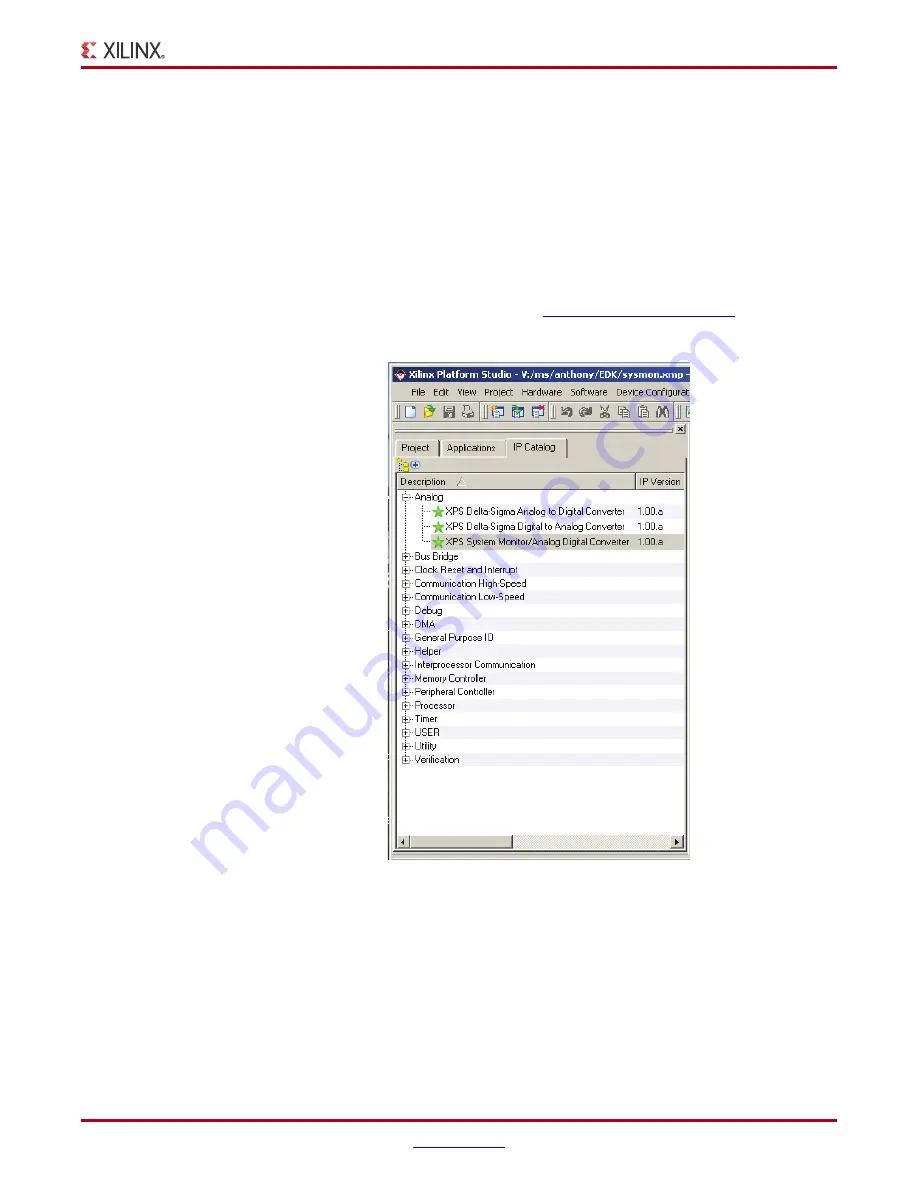

An Analog-to-Digital Converter (ADC) is a common microprocessor peripheral. Starting

with EDK 9.2i software, the Xilinx Embedded Development Kit (EDK) includes IP that

allows designers to easily connect System Monitor to the Processor Local Bus (PLB). The IP

is also supported with software drivers that allow application code to be quickly

developed. The System Monitor IP can be found in the IP Catalog under Analog (see

). It is possible to use System Monitor as a general-purpose ADC in an application

by disabling the monitoring of the on-chip sensors. The basic System Monitor functionality

can also be extended by the processor to include custom functionality and support various

communication protocols for system management or monitoring (e.g., Ethernet, UART,

and I

2

C). Refer to the EDK documentation at

for more

information.

X-Ref Target - Figure 32

Figure 32:

System Monitor can be found under Analog in the EDK IP Catalog

UG

3

70_

3

2_

060

8

09

www.BDTIC.com/XILINX