38

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

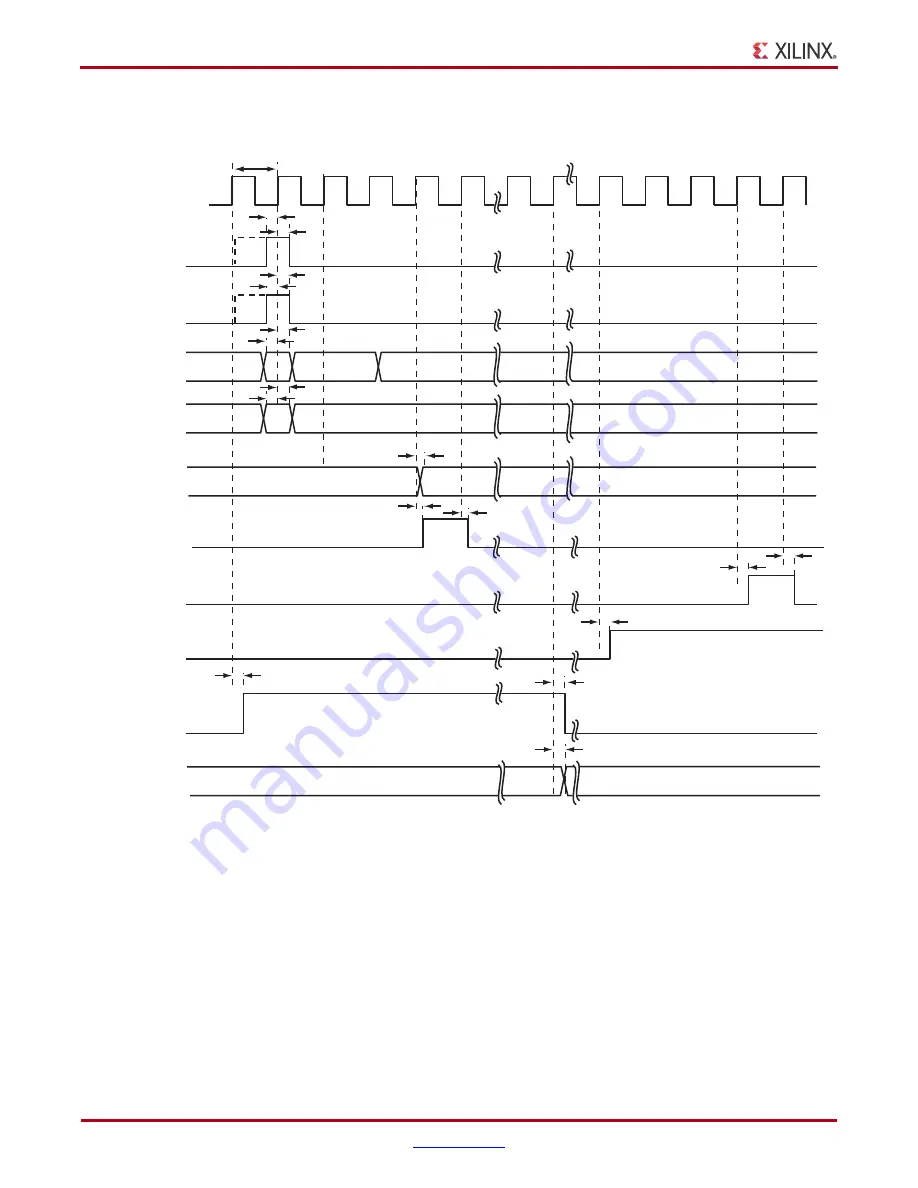

System Monitor Timing

describes the timing events shown in

.

X-Ref Target - Figure 16

Figure 16:

System Monitor Detailed Timing

t

5

t

9

t

8

t

10

t

7

t

6

t

4

t

2

t

1

t

3

DCLK

1

2

3

4

5

DWE

DEN

DADDR[6:0]

DI[15:0]

DO[15:0]

DRDY

t

11

t

11

t

13

t

14

t

14

t

15

t

12

t

12

EOC/EOS

ALM[2:0]/OT

BUSY

CHANNEL[4:0]

UG370_16_060809

www.BDTIC.com/XILINX