48

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

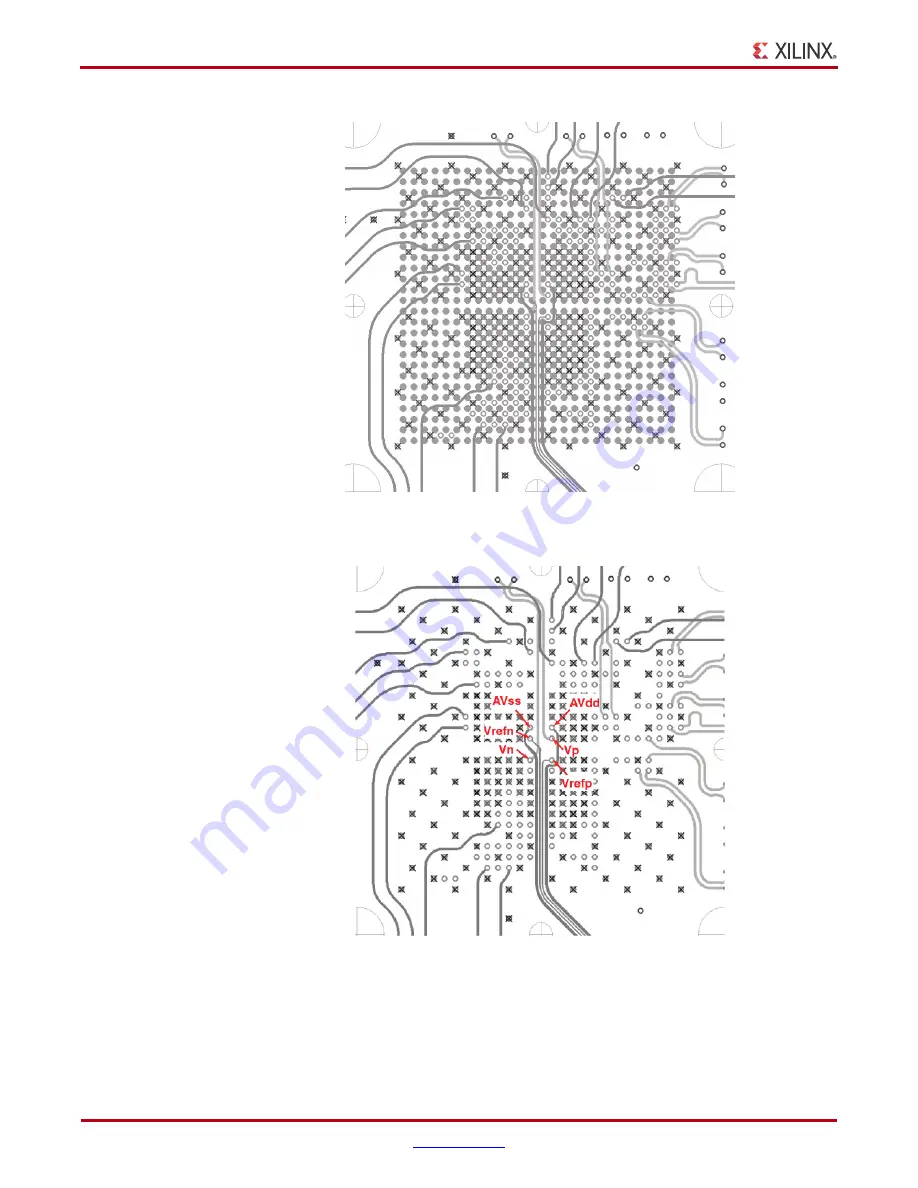

Application Guidelines

, the pads have been removed for clarity. The reference inputs (V

REFP

and

V

REFN

) are routed as a tightly coupled differential pair from an external 1.25V reference IC

at the bottom edge of the FPGA (refer to

for the connections). The

X-Ref Target - Figure 27

Figure 27:

Routing Channels to Center of Array Created by Staggering Vias

X-Ref Target - Figure 28

Figure 28:

Reference Inputs (V

REFP

and V

REFN

) should be Routed as Differential

Pairs into the Center of the BGA

UG

3

70_27_060

8

09

UG

3

70_2

8

_

060

8

09

www.BDTIC.com/XILINX