19

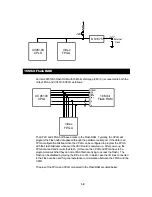

The FPGA enables the transmitter with TX_EN and sends bits on TXD

4-0

in sync with the

transmit clock (TX_CLK) generated by the PHY chip. The PHY chip is alerted to

transmission errors that occur in the MAC when the TX_ERR signal is asserted. The

FPGA also receives an indication when valid data has been received (RX_DV) and the

data (RXD

0-4

) in sync with the receiver clock (RX_CLK) from the PHY chip. Any reception

errors are indicated to the FPGA via the RX_ER signal. The CRS signal indicates when

the receiver is non-idle. The COL signal is asserted when data collides on the Ethernet.

The FPGA can disable the interface to the PHY chip by asserting the tristate control

(TRSTE). Otherwise, the FPGA passes management information to and from the PHY

chip over the serial data line (MDIO) in sync with a clock (MDC). the FPGA can be alerted

to changes in PHY chip status by the FDS/MDINT interrupt line.

The CPLD sets the static values on pins which control the configuration of the PHY chip.

Pins MF0-4 set the modes for auto-negotiation, repeating, symbol transmission,

scrambling, etc. Likewise, the configurations signals (CFG0-1) select the 10 Mbps or 100

Mbps operating speed of the PHY chip. MDDIS enables/disables the management

information interface. FDE selects either full-duplex or half-duplex communication mode.

The reset (/RESET) and power-down (PWRDWN) signals do exactly what they say.

The CPLD also gets receives the status outputs from the PHY chip that normally drive

LEDs. The outputs are active-low and indicate when 100 Mbps operation is selected

(/LEDS), the receiver is active (/LEDR), the transmitter is active (/LEDT), the link is active

(/LEDL), and a collision is detected (/LEDC). The CPLD can relay these signals to the

LEDs on the XSV Board if you wish to display the Ethernet status.

XC95108

CPLD

LXT970A

Ethernet

PHY

Virtex

FPGA

mf

0 - 4

cfg

0 - 1

mddis

tpop

tpip

tpon

tpin

mdc

fds/mdint

trste

crs

col

rxd

0 - 4

rx_dv

mdio

rx_clk

rx_er

txd

0 - 4

tx_en

tx_clk

tx_err

fde

pwrdwn

leds

ledr

ledt

ledl

ledc

reset

4

4

4

2

RJ45

Connector

(J3)

tr

a

n

s

fo

rm

e

r

Summary of Contents for XSV

Page 8: ...7...

Page 34: ...33 B XSV Schematics The following pages show the detailed schematics for the XSV Board...

Page 35: ......

Page 36: ......

Page 37: ......

Page 38: ......

Page 39: ......

Page 40: ......

Page 41: ......

Page 42: ......

Page 43: ......

Page 44: ......

Page 45: ......

Page 46: ......

Page 47: ......

Page 48: ......

Page 49: ......

Page 50: ...XSV Board V0 1 Layout...