+5V_USB

DM

PUR

WKUP

RST

VREGEN

SUSP

CLKOUT

/CTS

/DSR

SIN

/DCD

RI

GPIO1

GPIO2

GPIO3

GPIO4

SDA

SOUT

DTR

R

TS

/DCD

SIN

/DSR

GPIO1

GPIO2

GPIO3

GPIO4

RI

R

TS

DTR

SOUT

/CTS

DP

X1

X2

+3.3V_USB

+3.3V_USB

+3.3V_USB

+3.3V_USB

+3.3V_USB

+3.3V_USB

+3.3V

+3.3V

+3.3V

R

TS

DTR

SOUT

GPIO1

GPIO3

GPIO4

GPIO2

/CTS

/DSR

SIN

/DCD

RI

/CTS

/DSR

SIN

/DCD

GPIO1

GPIO2

GPIO3

GPIO4

RI

R

TS

DTR

SOUT

FPGA_PDN

SH4

FPGA_SEN

SH4

FPGA_SCLK

SH4

FPGA_RST

SH4

FPGA_SDA

T

A

SH4

CH8-D13

SH5

CH8-D12

SH5

CH8-D1

1

SH5

CH8-D8

SH5

CH8-D10

SH5

CH8-D9

SH5

CH8-D0

SH5

CH8-D1

SH5

CH8-CLKOUT

SH5

CH8-D5

SH5

CH8-D2

SH5

CH8-D3

SH5

CH8-D4

SH5

CH8-D6

SH5

CH8-D7

SH5

24LC32A

Donotinstalled

Donotinstalled

Donotinstalled

R23

1.5K

R23

1.5K

SW4

RESET

SW4

RESET

1

2

R46

1K

R46

1K

TP7TP7

J16J16

1

2

U8

EEPROM32K(4Kx8)

U8

EEPROM32K(4Kx8)

A1

1

A2

2

A3

3

SDA

5

GND

4

SCL

6

WP

7

VCC

8

R18

100K

R18

100K

L3

1K@100MHZ

L3

1K@100MHZ

1

2

R25

33ohm

R25

33ohm

C77

22pF

C77

22pF

C78

22pF

C78

22pF

R24

15K

R24

15K

Y1

12MHzw/18pF

Y1

12MHzw/18pF

1

3

2

4

R21

4.99K

R21

4.99K

R22

33K

R22

33K

C73

33pF

C73

33pF

U5

TPS76933DBVT

U5

TPS76933DBVT

EN

3

IN

1

GND

2

OUT

5

NC/FB

4

R43

10K

R43

10K

C74

1000pF

C74

1000pF

U6

TUSB3410IVF

U6

TUSB3410IVF

SOUT/IR_SOUT

19

X1/CLKI

27

SCL

1

1

DTR*

21

W

AKEUP*

12

RESET*

9

VD

D1

8

4

CTS*

13

SUSPEND

2

DP

6

PUR

5

CLKOUT

22

VREGEN*

1

DM

7

GN

D1

8

18

R

TS*

20

TEST1

24

DSR*

14

TEST0

23

VC

C3

3

SIN/IR_SIN

17

P3.4

29

SDA

10

GN

D8

8

P3.3

30

P3.1

31

P3.0

32

GN

D2

8

28

X2

26

RI*/CP

16

DCD*

15

VC

C2

5

25

U1-4

XC4VLX25-SF363-BGA

U1-4

XC4VLX25-SF363-BGA

IO_L20P_7

R19

IO_L20N_VREF_7

R20

IO_L21P_7

R15

IO_L21N_7

R16

IO_L23P_VRN_7

T19

IO_L23N_VRP_7

T20

IO_L24P_CC_LC_7

R17

IO_L24N_CC_LC_7

R18

IO_L25P_CC_SM7_LC_7

T17

IO_L25N_CC_SM7_LC_7

T18

IO_L26P_SM6_7

U18

IO_L26N_SM6_7

U19

IO_L27P_SM5_7

T15

IO_L27N_SM5_7

U15

IO_L28P_7

V19

IO_L28N_VREF_7

V20

IO_L29P_SM4_7

U16

IO_L29N_SM4_7

U17

IO_L30P_SM3_7

W18

IO_L30N_SM3_7

W19

IO_L31P_SM2_7

Y17

IO_L31N_SM2_7

W17

IO_L32P_SM1_7

V17

IO_L32N_SM1_N_7

V18

IO_L25P_CC_LC_8

U3

IO_L25N_CC_LC_8

U2

IO_L26P_8

T4

IO_L26N_8

T3

IO_L27P_8

T6

IO_L27N_8

U6

IO_L28P_8

V2

IO_L28N_VREF_8

V1

IO_L29P_8

U5

IO_L29N_8

U4

IO_L30P_8

W3

IO_L30N_8

W2

IO_L31P_8

Y4

IO_L31N_8

W4

IO_L32P_8

V4

IO_L32N_8

V3

IO_L20P_8

R2

IO_L20N_VREF_8

R1

IO_L21P_8

R6

IO_L21N_8

R5

IO_L23P_VRN_8

T2

IO_L23N_VRP_8

T1

IO_L24P_CC_LC_8

R4

IO_L24N_CC_LC_8

R3

R38

1K

R38

1K

C75

33pF

C75

33pF

R42

330

R42

330

C71

4.7uF

C71

4.7uF

R44

10K

R44

10K

R40

330

R40

330

R47

1K

R47

1K

C72

10uF

C72

10uF

R20

10K

R20

10K

R19

90.9K

R19

90.9K

D1

GREEN

D1

GREEN

R41

330

R41

330

D2

GREEN

D2

GREEN

D4

GREEN

D4

GREEN

R39

330

R39

330

R37

1K

R37

1K

J8

CONNUSB

TYP

BFEM

J8

CONNUSB

TYP

BFEM

1

2

3

4

R26

33ohm

R26

33ohm

SW5

RESET

SW5

RESET

1

2

D5

DIODE

D5

DIODE

D3

GREEN

D3

GREEN

C76

1uF

C76

1uF

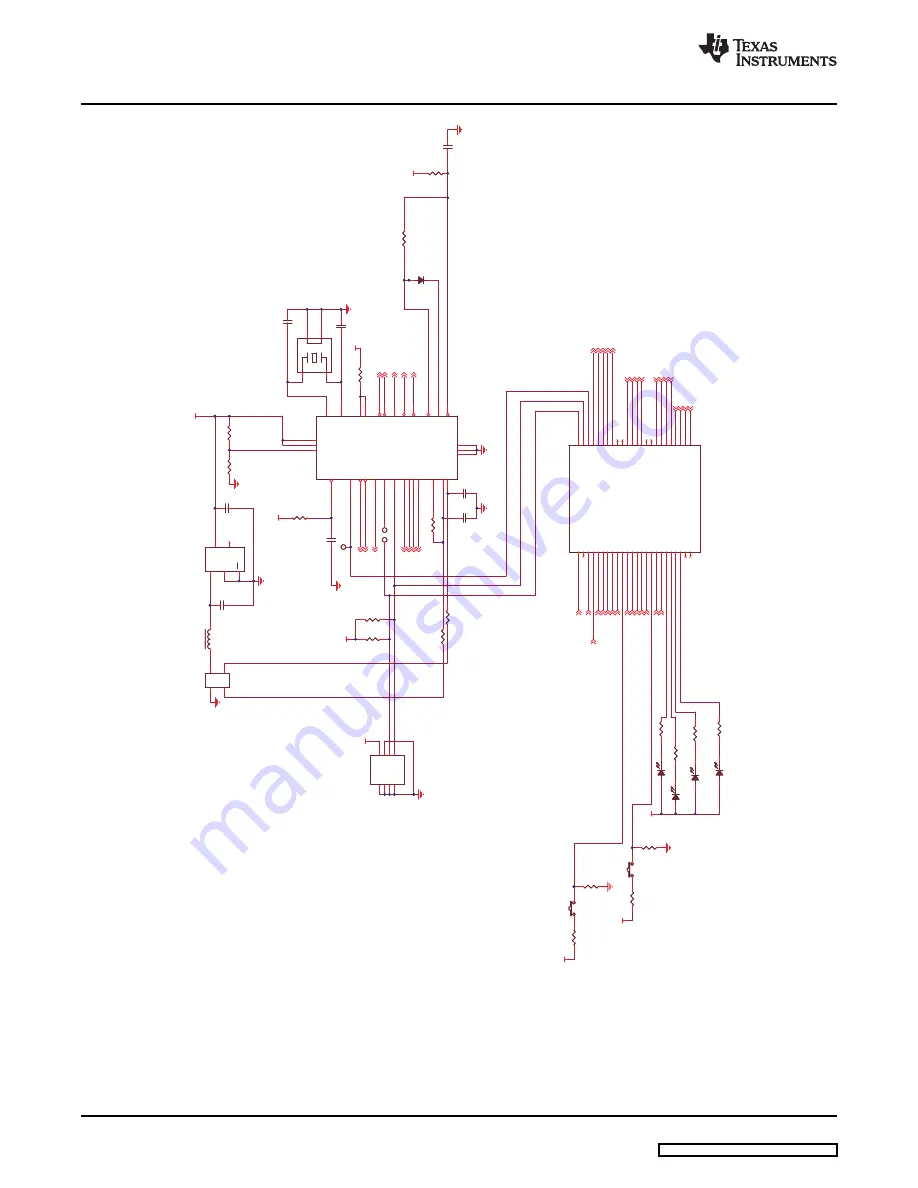

Schematics and Bill of Materials

www.ti.com

Figure 14. Schematic Diagram Page 2

24

TSW1200EVM: High-Speed LVDS Deserializer and Analysis System

SLAU212A – April 2007 – Revised August 2008