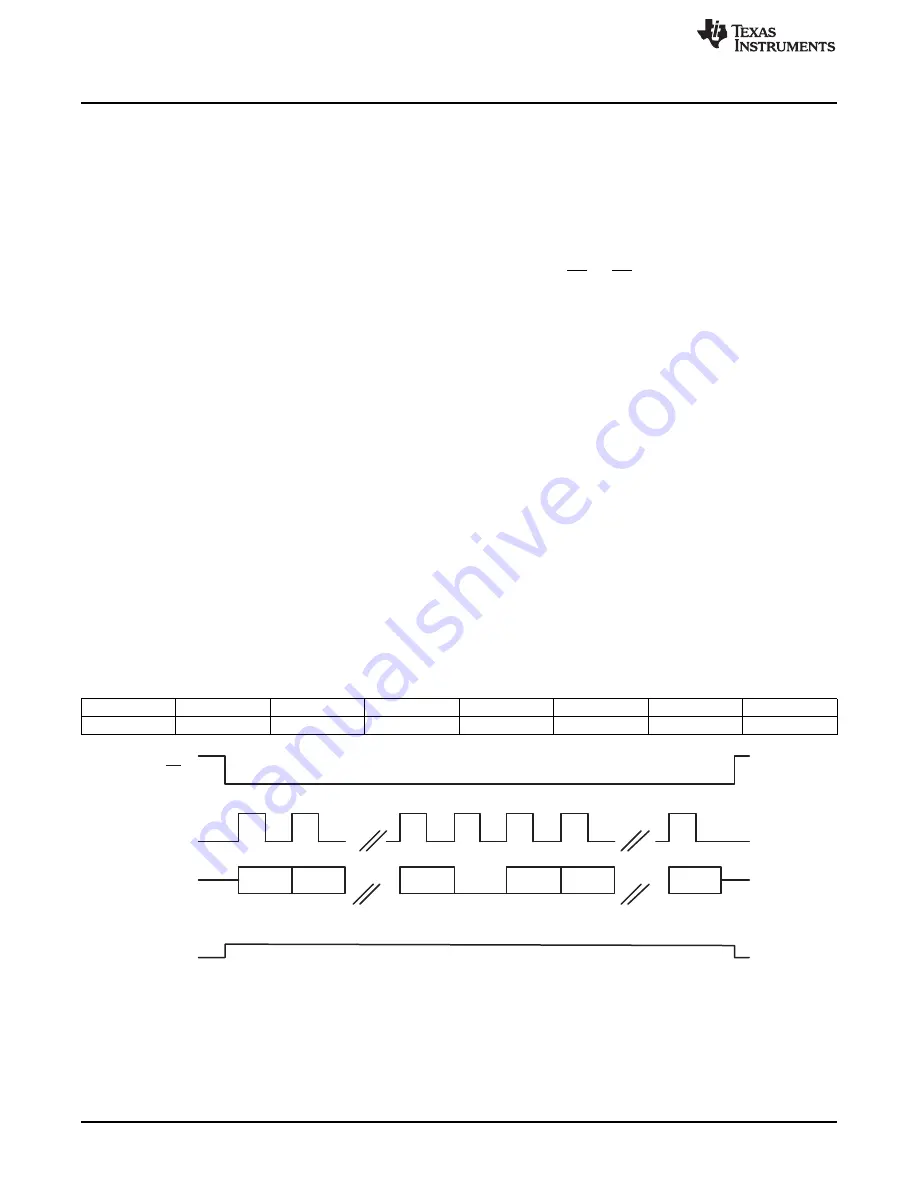

RA(6)

RA(5)

RA(0)

D(7)

D(6)

D(0)

7-bit Register Address

Write

8-bit Register Data

SS

SCLK

MOSI

MISO

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Control Interfaces

In the case of an I

2

C register write, if the master does not issue a STOP condition, then the device enters

auto-increment mode. So in the next eight clocks, the data on SDA is treated as data for the next

incremental register.

Similarly, in the case of an I

2

C register read, after the device has sent out the 8-bit data from the

addressed register, if the master issues a ACKNOWLEDGE, the slave takes over control of SDA bus and

transmit for the next 8 clocks the data of the next incremental register.

2.8.2 SPI Digital Interface

In the SPI control mode, the TLV320DAC3203 uses the pins SCL/SS as SS, SCLK as SCLK, MISO as

MISO, SDA/MOSI as MOSI; a standard SPI port with clock polarity setting of 0 (typical microprocessor

SPI control bit CPOL = 0). The SPI port allows full-duplex, synchronous, serial communication between a

host processor (the master) and peripheral devices (slaves). The SPI master (in this case, the host

processor) generates the synchronizing clock (driven onto SCLK) and initiates transmissions. The SPI

slave devices (such as the TLV320DAC3203) depend on a master to start and synchronize transmissions.

A transmission begins when initiated by an SPI master. The byte from the SPI master begins shifting in on

the slave MOSI pin under the control of the master serial clock (driven onto SCLK). As the byte shifts in

on the MOSI pin, a byte shifts out on the MISO pin to the master shift register.

The TLV320DAC3203 interface is designed so that with a clock-phase bit setting of 1 (typical

microprocessor SPI control bit CPHA = 1), the master begins driving its MOSI pin and the slave begins

driving its MISO pin on the first serial clock edge. The SSZ pin can remain low between transmissions;

however, the TLV320DAC3203 only interprets the first 8 bits transmitted after the falling edge of SSZ as a

command byte, and the next 8 bits as a data byte only if writing to a register. Reserved register bits

should be written to their default values. The TLV320DAC3203 is entirely controlled by registers. Reading

and writing these registers is accomplished by an 8-bit command sent to the MOSI pin of the part prior to

the data for that register. The command is structured as shown in

. The first 7 bits specify the

register address which is being written or read, from 0 to 127 (decimal). The command word ends with an

R/W bit, which specifies the direction of data flow on the serial bus. In the case of a register write, the R/W

bit should be set to 0. A second byte of data is sent to the MOSI pin and contains the data to be written to

the register. Reading of registers is accomplished in similar fashion. The 8-bit command word sends the 7-

bit register address, followed by R/W bit = 1 to signify a register read is occurring. The 8-bit register data

is then clocked out of the part on the MISO pin during the second 8 SCLK clocks in the frame.

Table 2-24. SPI Command Word

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

ADDR(6)

ADDR(5)

ADDR(4)

ADDR(3)

ADDR(2)

ADDR(1)

ADDR(0)

R/WZ

Figure 2-50. SPI Timing Diagram for Register Write

68

TLV320DAC3203 Application

SLAU434 – May 2012

Copyright © 2012, Texas Instruments Incorporated