MSP430xG461x

MIXED SIGNAL MICROCONTROLLER

SLAS508I − APRIL 2006 − REVISED MARCH 2011

88

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

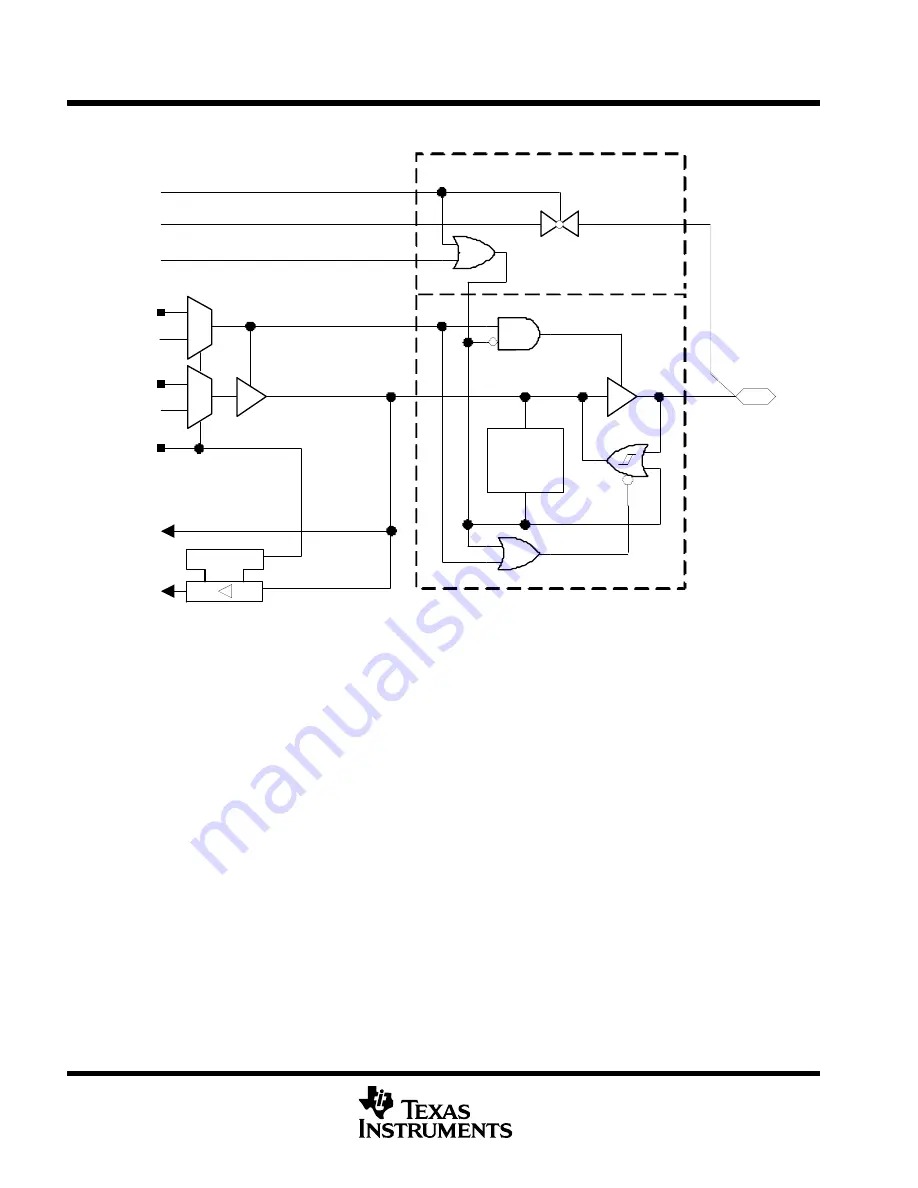

port P7, P7.0 to P7.3, input/output with Schmitt trigger

Bus

Keeper

EN

Direction

0: Input

1: Output

P7SEL.x

1

0

P7DIR.x

P7IN.x

LCDS28/32

Segment Sy

Pad Logic

DVSS

D

EN

Module X IN

1

0

Module X OUT

P7OUT.x

P7.3/UCA0CLK/S30

P7.2/UCA0SOMI/S31

P7.1/UCA0SIMO/S32

P7.0/UCA0STE/S33

Direction control

from Module X

Note: x = 0, 1, 2, 3

y = 30, 31, 32, 33

Summary of Contents for MSP430CG4616IPZ

Page 110: ......