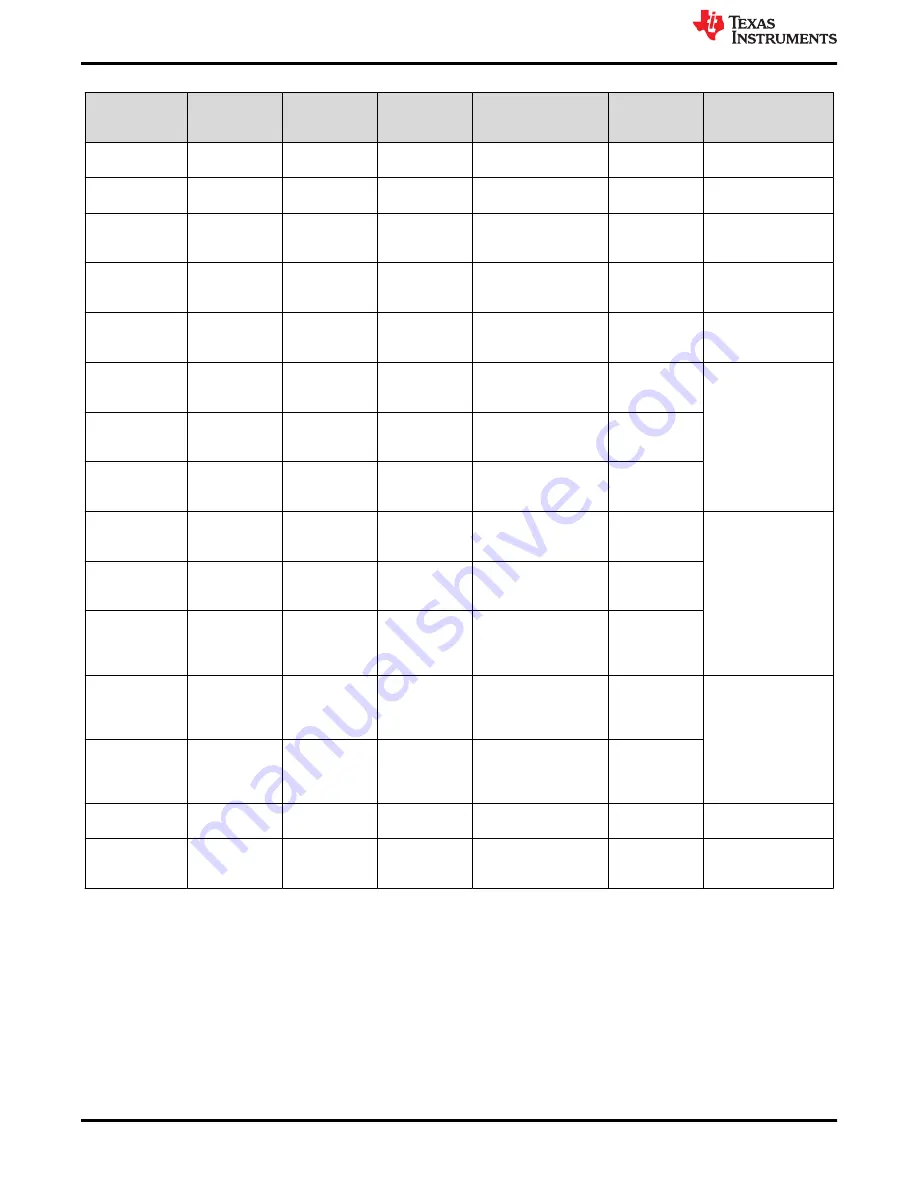

Table 6-1. State Transition Triggers (continued)

Trigger

Priority (ID)

Immediate

(IMM)

REENTERANT

PFSM Current State

PFSM

Destination

State

Power Sequence or

Function Executed

SOC Power

10

False

False

ACTIVE

MCU ONLY

PWR_SOC_ERR

I2C_1 bit is

11

False

True

ACTIVE, MCU ONLY

No State

Change

Execute RUNTIME

BIST

I2C_2 bit is

12

False

True

ACTIVE, MCU ONLY

No State

Change

Enable I

2

C CRC on

I

2

C1 and I

2

C2 on all

GPIO2 Falling

Edge

13

False

False

ACTIVE

No State

Change

TPS65941111-Q1

LDO1 output is 3.3 V

in BYPASS mode

GPIO2 Rising

Edge

14

False

False

ACTIVE

No State

Change

TPS65941111-Q1

LDO1 output is 1.8 V

in LDO mode

ON Request

15

False

False

STANDBY, ACTIVE,

MCU ONLY, Suspend-

to-RAM

ACTIVE

TO_ACTIVE

WKUP1 goes

high

16

False

False

STANDBY, ACTIVE,

MCU ONLY, Suspend-

to-RAM

ACTIVE

NSLEEP1 and

NSLEEP2 are

17

False

False

STANDBY, ACTIVE,

MCU ONLY, Suspend-

to-RAM

ACTIVE

MCU ON

Request

18

False

False

STANDBY, ACTIVE

,

MCU ONLY, Suspend-

to-RAM

MCU ONLY

TO_MCU

WKUP2 goes

high

19

False

False

STANDBY, ACTIVE,

MCU ONLY, Suspend-

to-RAM

MCU ONLY

NSLEEP1 goes

low and

NSLEEP2 goes

20

False

False

ACTIVE, MCU ONLY,

Suspend-to-RAM

MCU ONLY

NSLEEP1 goes

low and

NSLEEP2 goes

low

21

False

False

ACTIVE, MCU ONLY

Suspend-to-

RAM

TO_RETENTION

NSLEEP1 goes

high and

NSLEEP2 goes

low

22

False

False

ACTIVE, MCU ONLY

Suspend-to-

RAM

I2C_0 bit goes

False

False

STANDBY, ACTIVE,

MCU ONLY

LP_STANDBY

TO_STANDBY

I2C_3 bit goes

False

False

ACTIVE, MCU ONLY

No State

Change

Devices are prepared

for OTA NVM update.

(1)

From the SAFE state, the PFSM automatically transitions to the hardware FSM state of SAFE_RECOVERY. From

the SAFE_RECOVERY state, the recovery counter is incremented and compared to the recovery count threshold (see

RECOV_CNT_REG_2, in

). If the recovery count threshold is reached, then the PMICs halt recovery attempts and require a

power cycle. Refer to the

(2)

If the LP_STANDBY_SEL bit is set in the TPS65941213-Q1 (see RTC_CTRL_2, in

), then the PFSM transitions to the

hardware FSM state of LP_STANDBY. When LP_STANDBY is entered, then please use the appropriate mechanism to wakeup the

device as determined by the means of entering LP_STANDBY. Refer to the

for more details. LP_STANDBY_SEL in the

TPS65941111-Q1 is not applicable to the PFSM triggers.

(3)

I2C_0, I2C_1, I2C_2 and I2C_3 are self-clearing triggers.

(4)

Enabling the I

2

C CRC, enables the CRC on both I2C1 and I2C2, however, the I2C2 is disabled for 2ms after the CRC is enabled. Be

aware when using the watchdog Q&A before enabling I

2

C CRC. The recommendation is to enable the I

2

C CRC first, and then after

2ms, start the watchdog Q&A.

(5)

NSLEEP1 and NSLEEP2 of the primary PMIC can be accessed through the GPIO pin or through a register bit. If either the register bit

or the GPIO pin is pulled high, the NSLEEPx value is read as a

high

logic level.

Pre-Configurable Finite State Machine (PFSM) Settings

34

Optimized Dual TPS6594-Q1 PMIC User Guide for Jacinto

™

7 DRA829 or

TDA4VM Automotive PDN-0C

SLVUC99 – JANUARY 2022

Copyright © 2022 Texas Instruments Incorporated