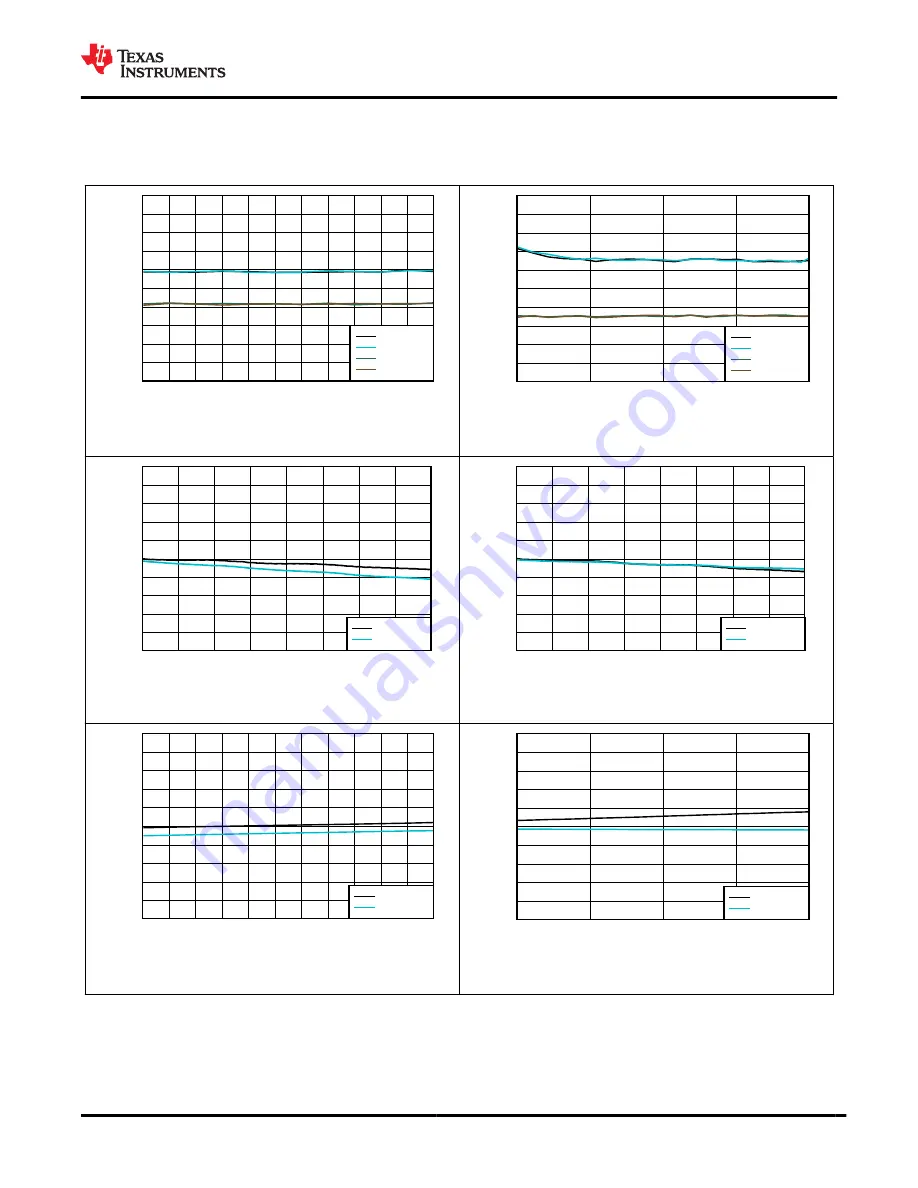

6.17 Typical Characteristics: Voltage Output (continued)

at T

A

= 25°C, V

DD

= 5.5 V, external reference = 5.5 V, gain = 1x, 12-bit resolution, and DAC outputs unloaded (unless

otherwise noted)

Temperature (

C)

V

oltage Ou

tput D

NL (LS

B)

-40

-25

-10

5

20

35

50

65

80

95

110 125

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

CH1 MAX

CH0 MAX

CH1 MIN

CH0 MIN

Figure 6-10. Voltage Output DNL vs Temperature

Supply Voltage (V)

V

oltage Ou

tput D

NL (LS

B)

1.8

2.725

3.65

4.575

5.5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

CH1 MAX

CH0 MAX

CH1 MIN

CH0 MIN

Figure 6-11. Voltage Output DNL vs Supply Voltage

Code

V

oltage Ou

tput TUE (

%

FSR)

0

512

1024

1536

2048

2560

3072

3584

4095

-1.5

-1.2

-0.9

-0.6

-0.3

0

0.3

0.6

0.9

1.2

1.5

Channel 1

Channel 0

Internal reference, gain = 4x

Figure 6-12. Voltage Output TUE vs Digital Input Code

Code

V

oltage Ou

tput TUE (

%

FSR)

0

512

1024

1536

2048

2560

3072

3584

4095

-1.5

-1.2

-0.9

-0.6

-0.3

0

0.3

0.6

0.9

1.2

1.5

Channel 1

Channel 0

Figure 6-13. Voltage Output TUE vs Digital Input Code

Temperature (

C)

V

oltage Ou

tput TUE (

%

FSR)

-40

-25

-10

5

20

35

50

65

80

95

110 125

-1.5

-1.2

-0.9

-0.6

-0.3

0

0.3

0.6

0.9

1.2

1.5

Channel 1

Channel 0

DAC channels at midscale

Figure 6-14. Voltage Output TUE vs Temperature

Supply Voltage (V)

V

oltage Ou

tput TUE (

%

FSR)

1.8

2.725

3.65

4.575

5.5

-1.5

-1.2

-0.9

-0.6

-0.3

0

0.3

0.6

0.9

1.2

1.5

Channel 1

Channel 0

DAC channels at midscale

Figure 6-15. Voltage Output TUE vs Supply Voltage

SLASF47 – MAY 2022

Copyright © 2022 Texas Instruments Incorporated

15

Product Folder Links: