S50 Hardware User Guide

1VV0301505 Rev. 3

Page 15 of 60

2021-05-05

Not Subject to NDA

4.2.

Reset

S50 are equipped with circuitry for generating reset from two sources:

•

A reset is held active, when VSUP falls below the threshold of the brownout

detector (V

BOR =

1,2V … 1,7V), and is released when VSUP rises above V

BOR

+ V

HYST

.

The brownout detector also holds the reset active during power up, until VSUP >

V

BOR

.

•

A reset is generated, when VSUP is > V

BOR

and increases 300 mV or more, within

300 ms or less.

•

By holding pin B-1 (EXT-RES#) at

≤

VSUP*0,25V for t

HOLDRESETNORMAL

≥

0,2µs, an

external reset (

pin reset) is generated. This pin has a fixed internal pull-up

resistor (R

PU

= 11k

Ω

... 16k

Ω

). EXT-RES# may be left open if not used.

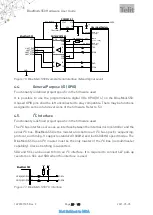

S50

E-6,F-6

VSUP

GND

+3V3

EXT-RES#

B-1

Reset-Switch is optional

Please Note: EXT-RES# of S50 has approx. 13k internal pullup.

Reset signal is optional

Host MCU

GPIO

VDD

Figure 4: S50 Example Reset

The following table shows the pin states of S50 during reset active. This pin

states are kept until hardware initialization has started.

Pin Name

State: S50

EXT-RES#

Input with pull-up

(1)

XL-IN

Input floating (disconnected)

XL-OUT

Input floating (disconnected)

UART-TXD

Input floating (disconnected)

UART-RXD

Input floating (disconnected)

UART-RTS#

Input floating (disconnected) with pull-up resistor 470k

Ω

(2)

UART-CTS#

Input floating (disconnected)

IUR-OUT#

Input floating (disconnected)

IUR-IN#

Input floating (disconnected)

GPIO[0:14]

Input floating (disconnected)