1-29

IC

VGN-

S36C/S36GP/S36LP/S36SP/S36TP/S38CP/

S52B/

S62PS/S62PSY/S62S/

S350F/S350FP/

S360/S360P/

S370F

(J/AM

/AO

)

Confidential

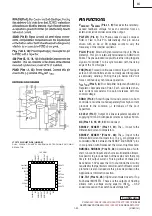

ELECTRICAL CHARACTERISTICS (continued)

(V+ = 15V, VCC = VDD =

SHDN

= 5V,

SKIP

= GND, TA = -40°C to +85°C, unless otherwise noted.) (Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

Minimum Off-Time

tOFF(MIN)

(Note 3)

500

ns

FB forced above the regulation point,

LSAT = GND

0.85

Quiescent Supply Current (VCC)

ICC

FB forced above the regulation point,

VLSAT > 0.5V

1.0

mA

Quiescent Supply Current (VDD)

IDD

FB forced above the regulation point

5

µA

Quiescent Supply Current (V+)

I V+

40

µA

Shutdown Supply Current (VCC)

SHDN

= GND

7

µA

Shutdown Supply Current (VDD)

SHDN

= GND

5

µA

Shutdown Supply Current (V+)

SHDN

= GND, V+ = 28V,

VCC = VDD = 0 or 5V

5

µA

REFERENCE

Reference Voltage

VREF

VCC = 4.5V to 5.5V, IREF = 0

1.980

2.020

V

REFIN Voltage Range

0.7

VREF

V

FAULT DETECTION

Overvoltage Trip Threshold

With respect to error comparator threshold,

OVP/UVP = VCC

10

20

%

Output Undervoltage Protection

Trip Threshold

With respect to error comparator threshold,

OVP/UVP = VCC

65

75

%

PGOOD Lower Trip Threshold

With respect to error comparator threshold,

hysteresis = 1%

-14

-6

%

PGOOD Upper Trip Threshold

With respect to error comparator threshold,

hysteresis = 1%

+6

+14

%

VCC Undervoltage Lockout

Threshold

VUVLO(VCC)

Rising edge, PWM disabled below this level

hysteresis = 20mV

4.1

4.4

V

CURRENT LIMIT

CSP

0

2.7

Current-Limit Input Range

CSN

-0.3

+28.0

V

Valley Current-Limit Threshold

(Fixed)

VLIM(VAL)

VCSP - VCSN, ILIM = VCC

35

65

mV

Valley Current-Limit Threshold

(Adjustable)

VLIM(VAL)

VCSP - VCSN, VILIM = 2.00V

160

240

mV

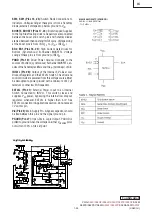

ELECTRICAL CHARACTERISTICS (continued)

(V+ = 15V, VCC = VDD =

SHDN

= 5V,

SKIP

= GND, TA = -40°C to +85°C, unless otherwise noted.) (Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

INPUTS AND OUTPUTS

Logic Input Threshold

SHDN

,

SKIP

, GATE

rising edge, hysteresis = 225mV

1.20

2.20

V

High

1.9

2.1

Dual Mode Threshold Voltage

MAX1992 FB

Low

0.05

0.15

V

High

VCC -

0.4V

Open

3.15

3.85

REF

1.65

2.35

Four-Level Input Logic Levels

TON, OVP/UVP,

LSAT, FBLANK

Low

0.5

V

Note 2: When the inductor is in continuous conduction, the output voltage has a DC regulation level higher than the error compara-

tor threshold by 50% of the output ripple. In discontinuous conduction (

SKIP

= GND, light load), the output voltage has a

DC regulation level higher than the trip level by approximately 1.5% due to slope compensation.

Note 3: On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = GND, V BST = 5V,

and a 250pF capacitor connected from DH to LX. Actual in-circuit times can differ due to MOSFET switching speeds.

Note 4: Specifications to -40 °C are guaranteed by design, not production tested.

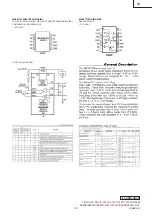

Pin Description

PIN

MAX1992

MAX1993

NAME

FUNCTION

1

1

TON

On-Time Selection Control Input. This four-level logic input sets the K-factor value

used to determine the DH on-time (see the On-Time One-Shot section). Connect to

analog ground (AGND or GND), REF, VCC, or leave TON unconnected to select the

following nominal switching frequencies:

VCC = 200kHz

Open = 300kHz

REF = 450kHz

AGND = 600kHz

2, 7, 8

—

N.C.

No Connection. Not internally connected.

—

2

FBLANK

Fault Blanking Control Input. This four-level logic input enables or disables fault

blanking, and sets the minimum forced-PWM operation time (t FBLANK). When fault

blanking is enabled, PGOOD, OVP protection, and UVP protection are blanked for the

selected time period after a transition is detected on GATE. Additionally, the controller

enters forced-PWM mode for the duration of t FBLANK anytime GATE changes states.

Connect FBLANK as follows:

VCC = 140µs (min) tFBLANK, fault blanking enabled

Open = 90µs (min) t FBLANK, fault blanking enabled

REF = 40µs (min) tFBLANK, fault blanking enabled

AGND = 90µs (min) tFBLANK, fault blanking disabled

Pin Description (continued)

PIN

MAX1992

MAX1993

NAME

FUNCTION

3

3

LSAT

Inductor Saturation Control Input. This four-level logic input sets the inductor current

saturation limit as a multiple of the valley current-limit threshold set by ILIM, or

disables the function if not required. Connect LSAT to the following pins to set the

saturation current limit:

VCC = 2

×

ILIM(VAL)

Open = 1.75

×

ILIM(VAL)

REF = 1.5

×

ILIM(VAL)

AGND = disable LSAT protection

See the Inductor Saturation Limit and Setting the Current Limit sections.

4

4

PGOOD

Open-Drain Power-Good Output. PGOOD is low when the output voltage is more than

10% (typ) above or below the normal regulation point, during soft-start, and in

shutdown. After the soft-start circuit has terminated, PGOOD becomes high

impedance if the output is in regulation. For the MAX1993, PGOOD is

blanked —forced high-impedance state —when FBLANK is enabled and the controller

detects a transition on GATE.

5

5

ILIM

Valley Current-Limit Threshold Adjustment. The valley current-limit threshold defaults

to 50mV if ILIM is tied to VCC. In adjustable mode, the valley current-limit threshold

across CSP and CSN is precisely 1/10th the voltage seen at ILIM over a 250mV to

2.5V range. The logic threshold for switchover to the 50mV default value is

approximately VCC - 1V. When the inductor saturation protection threshold is

exceeded, ILIM sinks 6µA. See the Current-Limit Protection (ILIM) section.

6

6

REF

2.0V Reference Voltage Output. Bypass REF to analog ground with a 0.1µF or greater

ceramic capacitor. The reference can source up to 50µA for external loads. Loading

REF degrades output voltage accuracy according to the REF load regulation error.

The reference is disabled when the MAX1992/MAX1993 is shut down.

—

7

REFIN

External Reference Input. REFIN sets the feedback regulation voltage (VFB = VREFIN)

of the MAX1993.

—

8

OD

Open-Drain Output. Controlled by GATE.

9

9

FB

Feedback Input.

MAX1992: Connect to VCC for a +1.8V fixed output or to AGND for a +2.5V fixed

output. For an adjustable output (0.7V to 5.5V), connect FB to a resistive divider from

the output voltage. The FB regulation level is +0.7V.

MAX1993: The FB regulation level is set by the voltage at REFIN.

10

10

OUT

Output Voltage Sense. Connect directly to the positive terminal of the output

capacitors as shown in the standard application circuits (Figures 1 and 9). OUT

senses the output voltage to determine the on-time for the high-side switching

MOSFET. For the MAX1992, OUT also serves as the feedback input when using the

preset internal output voltages as shown in Figure 7. When discharge mode is

enabled by OVP/UVP, the output capacitor is discharged through an internal 10

Ω

resistor connected between OUT and ground.

11

11

CSP

Positive Current-Sense Input. Connect to the positive terminal of the current-sense

element. Figure 10 and Table 7 describe several current-sensing options. The PWM

controller does not begin a cycle unless the current sensed is less than the valley

current-limit threshold programmed at ILIM.

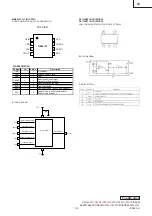

Pin Description (continued)

PIN

MAX1992

MAX1993

NAME

FUNCTION

12

12

CSN

Negative Current-Sense Input. Connect to the negative terminal of the current-sense

element. Figure 10 and Table 7 describe several current-sensing options. The PWM

controller does not begin a cycle unless the current sensed is less than the valley

current-limit threshold programmed at ILIM.

13

13

SKIP

Pulse-Skipping Control Input. Connect

SKIP

to VCC for low-noise, forced-PWM mode

or connect

SKIP

to analog ground (AGND or GND) to enable pulse-skipping

operation.

14

14

V+

Battery Voltage-Sense Connection. The controller only uses V+ to set the on-time one-

shot timing. The DH on-time is inversely proportional to input voltage over a range of

2V to 28V.

15

15

DH

High-Side Gate-Driver Output. DH swings from LX to BST.

16

16

LX

Inductor Connection. Connect LX to the switched side of the inductor. LX serves as

the lower supply rail for the DH high-side gate driver.

17

17

BST

Boost Flying Capacitor Connection. Connect to an external capacitor and diode as

shown in Figure 6. An optional resistor in series with BST allows the DH pullup current

to be adjusted.

18

18

DL

Low-Side Gate-Driver Output. DL swings from PGND to VDD (MAX1992) or GND to

VDD (MAX1993).

19

19

VDD

Supply Voltage Input for the DL Gate Driver. Connect to the system supply voltage

(+4.5V to +5.5V). Bypass VDD to PGND with a 1µF or greater ceramic capacitor.

20

—

PGND

Power Ground. Ground connection for the DL low-side gate driver.

—

20

GND

Analog and Power Ground. AGND and PGND connect together internally. Connect

backside pad to GND.

21

—

AGND

Analog Ground. Connect backside pad to AGND.

—

21

GATE

Buffered N-Channel MOSFET Gate Input. A logic low on GATE turns off the internal

MOSFET so OD appears as a high impedance. A logic high on GATE turns on the

internal MOSFET, pulling OD to ground.

22

22

VCC

Analog Supply Input. Connect to the system supply voltage (+4.5V to +5.5V) through

a series 20

Ω

resistor. Bypass VCC to analog ground with a 1µF or greater ceramic

capacitor.

Pin Description (continued)

PIN

MAX1992

MAX1993

NAME

FUNCTION

23

23

SHDN

Shutdown Control Input. Connect to VCC for normal operation. Connect to analog

ground to put the controller into its 1µA shutdown state. When discharge mode is

enabled by OVP/UVP, the output is discharged through a 10

Ω

resistor between OUT

and ground, and DL is forced high after V OUT drops below 0.3V. When discharge

mode is disabled by OVP/UVP, OUT remains a high-impedance input and DL is

forced low, so LX also appears as a high-impedance input. A rising edge on

SHDN

clears the fault-protection latch.

24

24

OVP/UVP

Overvoltage/Undervoltage Protection and Discharge Mode Control Input. This four-

level logic input selects between various output fault-protection options (Table 6) by

selectively enabling OVP protection and UVP protection. When enabled, the OVP limit

defaults at 116% of the nominal output voltage, and the UVP limit defaults at 70% of

the nominal output voltage. Discharge mode is enabled when UVP protection is also

enabled. Connect OVP/UVP to the following pins for the desired function:

VCC = enable OVP and discharge mode, enable UVP

Open = enable OVP and discharge mode, disable UVP

REF = disable OVP and discharge mode, enable UVP

AGND = disable OVP and discharge mode, and UVP

See the Fault Protection and Shutdown and Output Discharge sections.