8

4. CIRCUIT DESCRIPTION

1. GENERAL

Circuit will be described in reference to the QD-101MM block diagram in Fig. 2.

Composite video signal which enters via pin jack connector is converted into the digital RGB

in the composite video input circuit by the control signal from the I

2

C bus controller. The signal

then enters the signal selector circuit.

Computer analog signal enters via the 15-pin connector and is processed through the computer

analog input circuit and the A/D conversion circuit. The signal is then converted into the digital

RGB signal and enters the signal selector circuit.

Digital video signal from IBM PC EGA or CGA enters via the 15-pin connector is input into the

signal selector circuit.

The signal selected in the signal selector circuit is written into the field memory. The writing

operation into the field memory is controlled by signals which are generated in the IC100 by

HSYNC. VSYNC. Since the LCD control is asynchronous with the computer signal, FRCK.

FRRS is generated in the IC100, and is read out at their timings.

The audio control circuit controls the audio signal input from the audio input terminal, according

to the control signal from IC100. IC400(MPU) controls IC100, IC107 (I

2

C bus controller) by the

key operation from SW PWB. Since control data from the key is stored into EEPROM, the set

data is memorized even if the power is turned off.

2. COMPUTER SIGNAL INPUT CIRCUIT

In addition to composite video signal, QD-101MM can receive the computer analog RGB signal

and the computer digital RGB signals of MDA, CGA, EGA. These signals enter each input

circuit via the 15-pin connector (J2), pin jack (CN600), and S-terminal(CN601). After they are

converted into the digital signals, they are input to the signal selector or directly to the signal

selector circuit.

Refer to MAIN CIRCUIT No.3.

2.1.Computer digital signal input circuit

The computer digital signal is input to Pins 2, 3, 4, 5, 12 and 15 of J2, and is directly sent to the

signal selector.

EGA outputs the video signal at the 6-bit TTL level. (R, G, B, r, g, b)

CGA outputs the video signal at the 4-bit TTL level. (R, G, B ,I)

MDA outputs the video signal at the 2-bit TTL level. (Mono, Video, I)

As basic, the pins of J2 output the following signals.

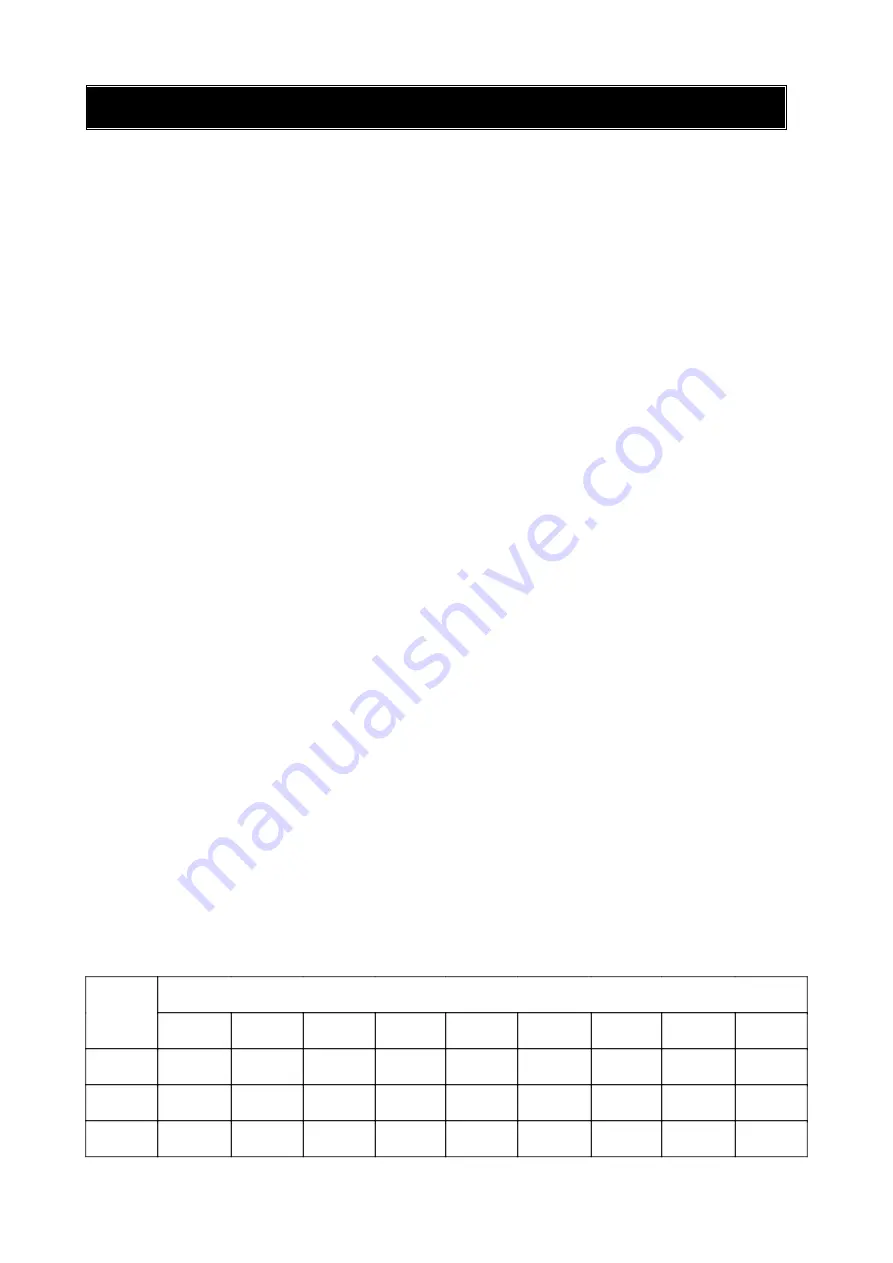

Table 1

x:Don`t care or N.C.

Signal

Connector J2's Pin Number

12

15

4

2

5

3

14

13

11

EGA

g

b

r

G

R

B

Vsync

Hsync

GND

CGA

I

x

x

G

R

B

Vsync

Hsync

GND

MDA

I

MONO

x

x

x

x

Vsync

Hsync

GND

Summary of Contents for QD-101MM

Page 39: ...38 6 CIRCUIT DIAGRAM PWB Fig 27 CIRCUIT DIAGRAM MAIN CIRCUIT No 1 ...

Page 40: ...39 Fig 27 CIRCUIT DIAGRAM MAIN CIRCUIT No 1 ...

Page 41: ...40 Fig 28 CIRCUIT DIAGRAM MAIN CIRCUIT No 2 ...

Page 42: ...41 Fig 28 CIRCUIT DIAGRAM MAIN CIRCUIT No 2 ...

Page 43: ...42 Fig 29 CIRCUIT DIAGRAM MAIN CIRCUIT No 3 ...

Page 44: ...43 Fig 29 CIRCUIT DIAGRAM MAIN CIRCUIT No 3 ...

Page 45: ...44 Fig 30 CIRCUIT DIAGRAM MAIN CIRCUIT No 4 ...

Page 46: ...45 Fig 30 CIRCUIT DIAGRAM MAIN CIRCUIT No 4 ...

Page 47: ...46 Fig 31 CIRCUIT DIAGRAM POWER CIRCUIT ...

Page 48: ...47 Fig 31 CIRCUIT DIAGRAM POWER CIRCUIT ...

Page 49: ...48 Fig 32 CIRCUIT DIAGRAM VIDEO CIRCUIT ...

Page 50: ...49 Fig 32 CIRCUIT DIAGRAM VIDEO CIRCUIT ...

Page 51: ...50 Fig 33 CIRCUIT DIAGRAM AUDIO CIRCUIT ...

Page 52: ...51 Fig 33 CIRCUIT DIAGRAM AUDIO CIRCUIT ...

Page 53: ...52 Fig 34 PWB PATTERN MAIN PWB FRONT SIDE ...

Page 54: ...53 Fig 34 PWB PATTERN MAIN PWB REAR SIDE ...

Page 66: ...PRINTED IN GERMANY ...