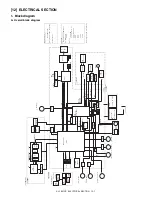

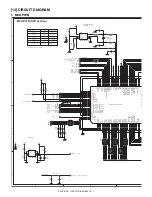

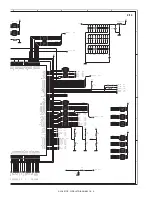

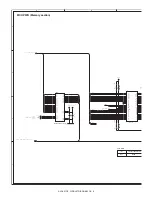

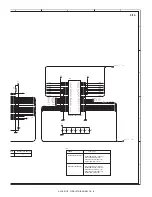

AL-1651CS CIRCUIT DIAGRAM 13 - 3

C53

47p

12

R29

33J

2

1

BR27

33J

1

2

3

4

8

7

6

5

C52

47p

12

C51

47p

12

C54

47p

12

R27

33J

2

1

C50

47p

12

C49

47p

12

R2

10K

2

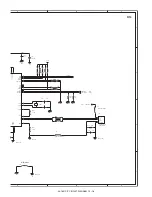

BR48

10kJ

1

2

3

4

8

7

6

5

BR61

10kJ

1

2

3

4

8

7

6

5

BR57

10kJ

1

2

3

4

8

7

6

5

BR53

10kJ

1

2

3

4

8

7

6

5

C67

0.1u

1

2

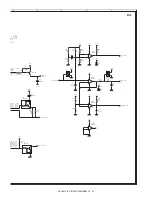

L3

ZJSR5101-223

1

2

3

X2

OSC-31

48MHz

N.C.

1

VCC

8

OUTPUT

5

GND

4

C68

12p

1

2

C66

22000p

1

2

R43

33J

2

1

C70

12p

1

2

C69

12p

1

2

R45

0J

2

1

X3

HC-49U/S (16.1511MHz)

12

R44

0J

2

1

R34

10kJ

2

1

BR33

10kJ

1

2

3

4

8

7

6

5

R33

10kJ

2

1

BR25

1

2

3

4

BR30

33J

1

2

3

4

8

7

6

5

R26

33J

2

1

R30

33J

2

1

R31

33J

2

1

R25

33J

2

1

R23

33J

2

1

BR39

33J

1

2

3

4

8

7

6

5

BR41

33J

1

2

3

4

8

7

6

5

BR43

33J

1

2

3

4

8

7

6

5

BR45

33J

1

2

3

4

8

7

6

5

BR49

33J

1

2

3

4

8

7

6

5

BR52

33J

1

2

3

4

8

7

6

5

BR56

33J

1

2

3

4

8

7

6

5

BR60

82J

1

2

3

4

8

7

6

5

BR62

33J

1

2

3

4

8

7

6

5

BR63

33J

1

2

3

4

8

7

6

5

R24

33J

2

1

C47

47p

12

C48

47p

12

BR29

10kJ

1

2

3

4

8

7

6

5

BR31

10kJ

1

2

3

4

8

7

6

5

R32

10kJ

2

1

BR93

1

2

3

4

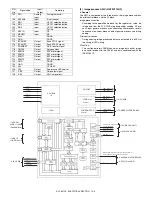

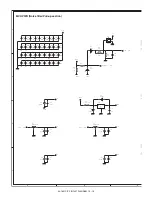

IC5

HG73C138HFV

ASIC

CPU_D

A

T

A

7

1

CPU_D

A

T

A

6

2

CPU_D

A

T

A

5

3

CPU_D

A

T

A

4

4

CPU_D

A

T

A

1

8

CPU_D

A

T

A

3

6

CPU_D

A

T

A

2

7

VCC(A

C)

5

CPU_D

A

T

A

0

9

GND(A

C)

10

MIRCNT

11

/CPUSYNC

12

MEM_INT

13

ARB_INT

14

VCC(CORE)

15

CPU_AD8

16

CPU_AD7

17

CPU_AD6

18

CPU_AD5

19

GND(CORE)

20

RAM_CLK_IN

21

CPU_AD4

22

CPU_AD3

23

CPU_AD2

24

CPU_AD1

25

CPU_AD0

26

/CPUCS

27

SFCLK48

28

GND(CORE)

29

/CPUWR

30

/CPURD

31

/RESET

32

PFCLK

34

CLKSW

35

GND(CORE)

36

PFCLK

OUT

37

PFCLKIN

38

GND(PLL)

39

VCC(PLL)

40

GND(PLL)

41

VCC(PLL)

42

TM2_15M

43

/SYNC

44

GND(A

C)

45

/VIDEO

46

/LEND

47

VCC(A

C)

48

OUTP00A

49

VCC(CORE)

192

/INREQ

191

/OUTCS

190

/OUT

A

C

K

189

/ESPRD

188

/F

AXPRD

187

/PCLPRD

186

GND(A

C)

185

MD

A

T15

184

MD

A

T14

183

MD

A

T13

182

VCC(CORE)

181

MD

A

T12

180

MD

A

T11

179

MD

A

T10

178

VCC(A

C)

177

MD

A

T09

176

MD

A

T08

175

MD

A

T07

174

G

ND

(CO

RE

)

173

RAM_DATA4

256

RAM_DATA5

255

RAM_DATA6

254

RAM_DATA7

253

GND(AC)

252

RAM_DQM0

251

RAM_WDE

250

VCC(AC)

249

RAM_CAS

248

RAM_RAS

247

RAM_CS

246

RAM_BANKS0

245

RAM_BANKS1

244

VCC(CORE)

243

RAM_MAD10

242

RAM_MAD0

241

RAM_MAD1

240

GND(CORE)

239

RAM_MAD2

238

RAM_MAD3

237

GND(AC)

236

MM_AI2

235

MM_AI1

234

MM_AI0

233

MM_PH_A

232

AFE_DB3

217

MM_BI2

231

MM_BI1

230

MM_Y2

225

VCC(A

C)

221

MM_Y1

226

AFE_DB0

220

AFE_DB1

219

GND(CORE)

223

AFE_DB2

218

AFE_DB4

216

AFE_DB5

215

MM_BI0

229

MM_PH_B

228

VCC(CORE)

227

MM_Y3

224

CLPWM

222

AFE_DB6

214

AFE_DB7

213

GND(A

C)

212

AFESCK

211

VCC(CORE)

210

ADCLK

209

GND(CORE)

208

AFE_SEN

207

CCD_PH1

206

CCD_PH2

205

AFE_SDI

204

CCD_CP

203

BSAMP

202

CCD_RS

201

CCD_TG

200

VSAMP

199

GND(CORE)

198

TD0

197

TRSK

195

TDI

196

TCK

193

TMS

194

VCC(CORE)

33

OUTP01A

50

GND(CORE)

257

RAM_DATA3

258

RAM_DATA2

259

RAM_DATA1

260

RAM_DATA0

261

GND(AC)

262

RAM_DATA15

263

RAM_DATA14

264

VCC(CORE)

265

RAM_DATA13

266

RAM_DATA12

267

RAM_DATA11

268

RAM_DATA10

269

RAM_DATA9

270

RAM_DATA8

271

VCC(CORE)

272

RAM_DQM1

273

RAM_CKE

274

GND(AC)

275

RAM_CLK_OUT

276

GND(CORE)

277

RAM_MAD12

278

RAM_MAD11

279

RAM_MAD9

280

VCC(CORE)

281

RAM_MAD8

282

RAM_MAD7

283

VCC(AC)

284

RAM_MAD6

285

RAM_MAD5

286

RAM_MAD4

287

GND(AC)

288

CPUDATA15

289

CPUDATA14

290

CPUDATA13

291

CPUDATA12

292

CPUDATA11

293

CPUDATA10

294

CPUDATA9

295

CPUDATA8

296

RAMDB0

RAMDB1

RAMDB2

RAMDB3

RAMDB4

RAMDB5

RAMDB6

RAMDB7

RAMDB15

RAMDB14

RAMDB13

RAMDB12

RAMDB11

RAMDB10

RAMDB9

RAMDB8

SFCLK48

PFCLKIN

PFCLKOUT

MM_BI2

MM_AI0

MM_BI1

MM_AI2

MM_BI0

MM_AI1

/INREQ

/OUTACK

/FAXPRO

/PCLPRO

/OUTCS

A8

D9

/OUTCS

/PCLPR

O

RAMDB13

D7

RAM_CLK_OUT

AFE_SDI

D4

D2

MEM_INT

RAMDB14

D8

PFCLKIN

/F

AXPR

O

D15

PFCLK

OUT

D3

D0

A7

A6

A5

CLKSW

RAMDB9

/INREQ

D1

D13

D5

JTG_TDI

D12

D11

RAMDB12

A4

A2

A1

/OUT

A

C

K

A9

A3

RAMDB1

D6

SFCLK48

RAMDB15

D10

PFCLK

SYNC#

D14

JTG_TDO

RAMDB2

/ESPRD

MAD8

MAD0

MAD10

MAD3

MAD2

MAD1

MAD6

MAD9

RAMDB7

RAMDB6

RAMDB5

RAMDB4

RAMDB3

RAMDB0

RAMDB11

RAMDB10

RAMDB8

MAD12

MAD11

MAD7

MAD5

MAD4

AFE_DB2

AFE_DB7

AFE_DB0

AFE_DB6

AFE_DB3

AFE_DB4

AFE_DB1

AFE_DB5

AFE_DB7

AFE_DB6

AFE_DB5

AFE_DB4

AFE_DB3

AFE_DB2

AFE_DB1

AFE_DB0

AFE_SDI

JTG_TMS

JTG_TCK

JTG_TDI

JTG_TMS

JTG_TCK

JTG_TDO

VCC3

VCC3

VCC3

VCC3

AFE_SEN

ADCLK

CCD_CP

CCD_PHI1

CCD_PHI2

CCD_TG

AFE_DB[7..0]

CL

CCD_RS

VSAMP

AFE_SCK

AFE_SDI

BSAMP

MM_Y1

MM_PH_A

MM_AI0

MM_AI1

MM_PH_B

MM_BI0

MM_BI1

MM_Y2

MM_Y3

BANK1

BANK0

/SDCAS

/SDRAS

/SDCS

DQM0

MAD[12..0]

/SDWDE

SDCKE

DQM1

SDCLK

D[15..0]

A[19..0]

/CS2

MIRCNT

CPU_SYNC

/L

WR

/RD

RAMDB[15..0]

PMD

ARB_INT

MMD

C

(/ASIC_RST)

/LEND

VIDEO#

/RESET0

(14-D3)

(1-D2),(14-D3)

(14-A3)

(14-A4)

(14-D3)

(14-A2)

(14-A2)

(14-D3)

(14-D3)

(14-A2)

(14-A2)

(14-A2)

(14-A2)

(5-B1)

(5-B1)

(6-B3)

(6-B3)

(6-B3)

(6-B3)

(6-B3)

(6-B3)

(5-B1)

(3-E2)

(3-E3)

(3-D2)

(3-D2)

(3-D2)

(3-D2)

(3-D2)

(3-D2)

(3-D2)

(3-E1)

(3-E2)

(3-E2)

(1-D2)

(1-C1)

IC5

(5-B1)

(1-A2)

(4-C3)

(1-D2)

(1-D2)

(1-B3)

(1-B3)

(1-B1)

(5-B1)

(5-B1)

()

(3-A1)

(4-A2)

(13-C2)

(3-A3)

(3-A2)

(13-B2)

(8-A1)

(4-C1)

(1-B1)

(9-B2)

(3-B2)

A

B

C

A

B

C

4

3

2

1

MCU PWB (ASIC section)