33 of 38

cRIO LVDT 9312 Module

Technical Description

Issue

05

24/05/2022

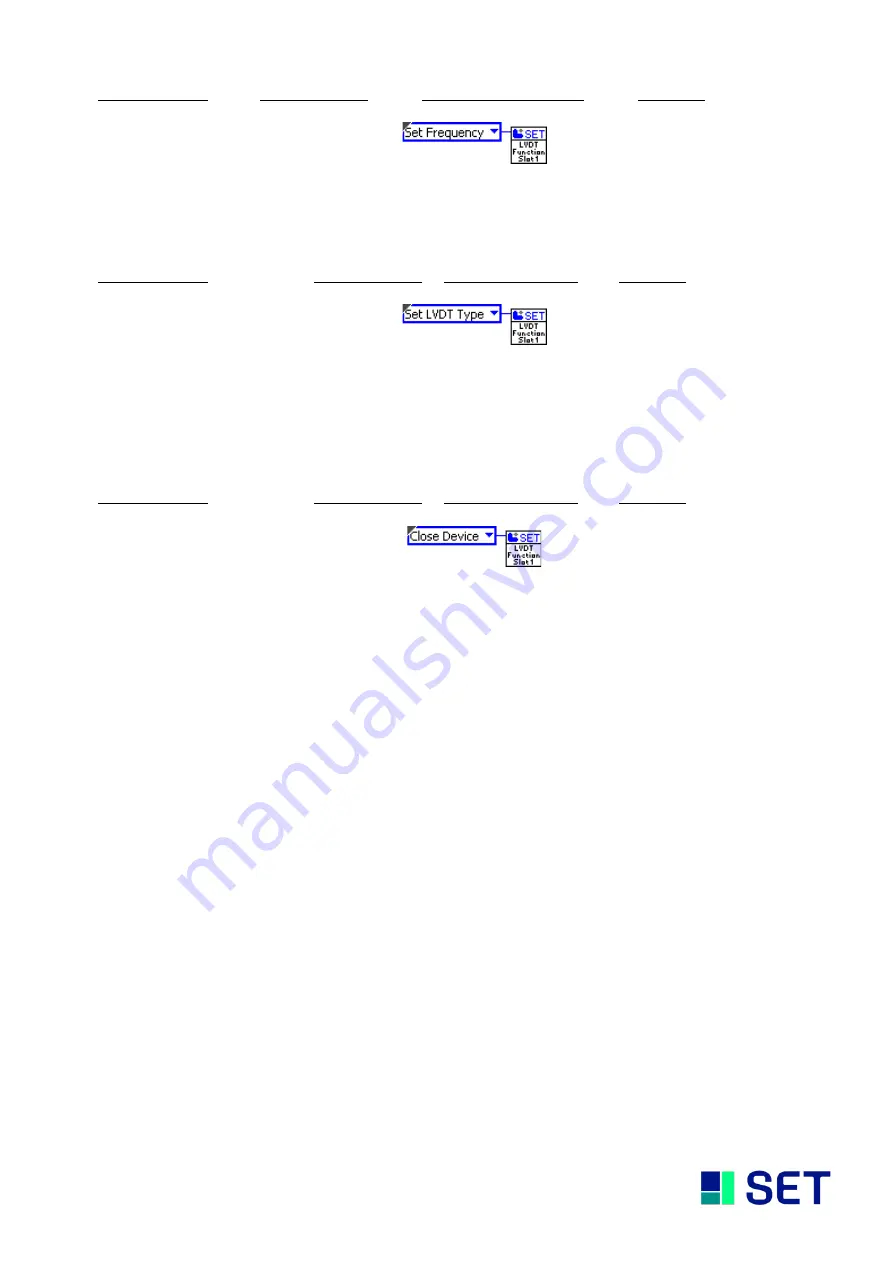

Instruction [U8]:

Tx-Data [U8]:

Receive-Data [U16]:

Data Sink:

Set Frequency

(10)

Exc. Freq.[Hz]

Exc. Freq.[Hz]

LVDT Controller

This instruction programs the excitation frequency. The data format is a 16bit engineering value with dimension

[Hz].

Valid Frequency Range: 1000 [Hz].. 10000 [Hz]

Instruction [U8]:

Tx-Data [U8]: Receive-Data [U16]: Data Sink:

Set LVDT Type

(8)

Res.Mode

Res.Mode

LVDT Controller

This instruction programs the demodulation stage. The data format is enumeration according to the following

table.

Valid position resolution data: Data = 0, 6 Wire LVDT demodulation

Data = 1, 4 Wire LVDT demodulation

Instruction [U8]:

Tx-Data [U8]: Receive-Data [U16]: Data Sink:

Close Device

(16)

No Data

No Data

FPGA Driver-VI

This instruction stops and terminates the applicable FPGA driver-VI.