Samsung Electronics

7-5

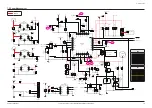

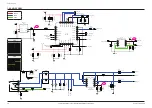

Schematic Diagram

This Document can not be used without Samsung’s authorization.

7-5 Power Management

LED+

EXT_PWR

CPU_RST

CHG_STATUS

V_DDCON

INN_BATT

P_3.0V

USB_P5V

P_1.0V

V_DDCON

R

62

9

5.

6K

R

61

0

12

0K

R

61

1

15

0K

GND

GND

GND

CHARGE_EN

PWR_ON_OFF

LED_DIMMING

PWR_IN_DDCON

C

62

0

10

00

0n

F

10

V

D601

KDS121V

C

62

3

10

00

0n

F

10

V

GND

RESET_IN

GND

R

62

3

10

K

GND

GND

R606

1K

C

61

0

10

0n

F

C

62

7

10

0n

F

C

61

9

10

0n

F

C

62

6

10

0n

F

C

61

6

10

0n

F

LE

D

-

LED_PWM

RESET_SW

P_3.0V

U601

MAX8819

1

C

O

M

P

4

2

F

B

4

3

O

V

P

4

4

P

G

4

5

LX

4

6

G

N

D

7

E

N

4

15

C

H

G

16

P

G

1

17

LX

1

18

P

V

13

19

LX

3

20

P

G

3

21

D

LI

M

1

22

FB2

23

FB3

24

EN123

25

PV2

26

LX2

27

PG2

28

DLIM2

12

CEN

10

SYS

8

RST1

13

FB1

11

DC

9

BAT

14

CISET

Q601

KTK5132V

1 Source

2

Gate

3 Drain

INN_BATT

I2C_DAT1

P_3.0V

GND

I2C_CLK1

GND

P_1.2V

P_1.8V

R

60

3

27

0K

R633

150

R632

150

INN_BATT

T601

PWR_SW

T602

RESET_SW

GND

R

61

6

39

K

R639

200K

P_3.0V

C

63

1

47

0n

F

10

V

R

64

1

20

0K

CORE_CTL

C

61

2

10

00

0n

F

10

V

Q602

KTK5132V

1

Source

2

Gate

3Drain

GND

P_3.0V

C

62

4

22

00

0n

F

6.

3V

C

61

8

10

00

nF

V

D

60

2

14

V

R618

4.7K

GND

VDDA_1.2V

R

62

4

56

K

R

62

5

27

0K

1%

GND

LP_CTL

C

63

0

10

0n

F

P_1.8V

U604

MAT

1 CTG

2 CELL

3 VDD

4 GND

5

SEO

6

EO

7

SCL

8

SDA

C

62

5

10

00

nF

L604

10uH

R

63

0

10

K

R

60

4

10

K

R

62

2

10

K

R631

100K

R

61

2

10

0K

R

64

0

10

0K

R

62

1

10

0K

R628

100K

C

61

5

22

00

0n

F

V_DDCON

V_DDCON

V_DDCON

GND

GND

R

60

9

10

K

R

61

3

10

K

P_1.8V

C

63

4

10

00

nF

R

60

7

10

0K

C

60

3

22

00

nF

P_2.5V

P_3.3V

P_3.0V

C

61

7

22

00

nF

C

63

2

22

00

nF

C

61

3

22

00

nF

U603

MIC5365-3.3YMT

1

VOUT

2

GND_1

3

EN

5

GND_2

4

VIN

U602

MIC5365-2.5YMT

1

VOUT

2

GND_1

3

EN

5

GND_2

4

VIN

U606

MIC5365-3.0YMT

1

VOUT

2

GND_1

3

EN

5

GND_2

4

VIN

L603

4.7uH

L6

01

4.

7u

H

L6

02

4.

7u

H

CON601

8P

1

2

3

4

5

6

7

8

R

61

5

10

K

C

60

8

22

nF

U605

RP100

1 VOUT

2 GND

3

CE

4

VDD

C

63

3

22

00

nF

C

60

4

22

00

nF

R

61

9

10

K

C

60

1

10

00

nF

10

V

V

D

60

1

14

V

R

61

4

1M

1%

GND

C

62

8

47

00

nF

R643

10K

C

60

6

47

00

nF

C611

4700nF

C

60

7

47

00

nF

C

62

9

22

00

0n

F

6.

3V

C609

100nF

R

60

8

20

0K

P3.3_CTL

D603

DSF05S30U

Q

60

3

R

N

19

07

F

E

1

2

3

4

5

6

R

60

1

47

K

GND

R

62

0

82

K

R

61

7

82

K

R

63

4

18

K

1/

16

W

3.0V

1% OK!

1% OK!

1% OK!

1%

O

K

1% OK

200ms delay

1% OK

400mA

300mA

300mA

1%

O

K

!

HIGH : 1.05V

LOW : 0.82V

CORE_CTL

1% OK!

1.5

===> 300mA

Current = 2000 x

R623

POWER

TP6

TP6

TP7

TP7

TP6

TP6

TP6

Summary of Contents for YP-R1

Page 15: ...3 4 Samsung Electronics MEMO ...

Page 44: ...Samsung Electronics 4 29 Troubleshooting Install completed Check device manager ...

Page 48: ...MEMO Samsung Electronics 4 33 ...

Page 53: ...5 5 Samsung Electronics MEMO ...

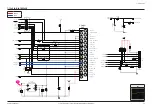

Page 58: ...Samsung Electronics 6 5 PCB Diagram 6 2 2 Test Point Wave Form TP2 TP3 TP4 TP7 TP6 ...

Page 59: ...6 6 Samsung Electronics MEMO ...

Page 69: ...7 10 Samsung Electronics MEMO ...