56

XW-NAC3-K

1

2

3

4

A

B

C

D

E

F

1

2

3

4

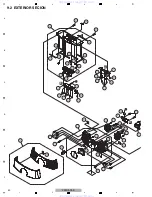

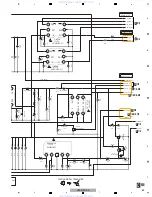

10.6 MAIN PCB ASSY (5/

8

)

C

5/8

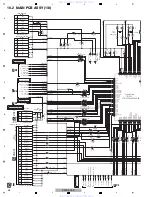

THIS I

N

TERCO

NN

ECTIO

N

DIAGRAM IS THE LATESET AT THE TIME

OF PRI

N

TI

N

G A

N

D SUBJECT TO CHA

N

GE

W

ITHOUT

N

OTICE.

N

OTE:

21

13

12

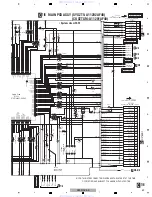

DSPDI

DSPDO

DSPHREQ

XDSPSS

DSPCK

DSPDO

DSPDI

XDSPRST

DATA1

XDSPSS

DSPCK

DSPHREQ

DATA0

SCLK

G

N

D

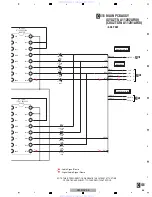

C2072

10 B

2125

C2073

10 B

2125

C2

0.1

C2

470

10

C2059

470P CH

1005

C2060

0.1 B

1005

C2061

470P CH

1005

C2062

0.1 B

1005

C2063

470P CH

1005

C2064

0.1 B

1005

IC2005

RP131H121D5-T1-F

1.25

V

REGURATOR

1

N

C

2G

N

D

3E

H

4

V

I

N

5

V

OUT

R2048

100 1/16

W

1005

R2073

10K 1/16

W

1005

R2049

100 1/16

W

1005

R2059

100K 1/16

W

1005

R2062

4.7K 1/16

W

1005

R2058

10K 1/16

W

1005

R2057

47 1/16

W

1005

R2047

100 1/16

W

1005

R2053

10K 1/16

W

1005

R2046

100 1/16

W

1005

R2045

100 1/16

W

1005

R2044

100K 1/16

W

1005

R2043

100K 1/16

W

1005

R2041

47K 1/16

W

1005

R2038

47 1/16

W

1005

R2037

47 1/16

W

1005

R2034

47 1/16

W

1005

G

N

D

(1;2;3;4;6;7;8)

DATA0

(4)

DATA1

(4)

LRCK

(4)

SCLK

(4)

XDSPRST

(1)

DSPDI

(1)

XDSPSS

(1)

DSPCK

(1)

DSPDO

(1)

DSPHREQ

(1)

IO_

V

DD

1

MODA_IRQA_

2

MODB_IRQB_PH1

3

MODC_IRQC_PH2

4

MODD_IRQD_PH3

5

CORE_

V

DD3

6

CORE_G

N

D3

7

HREQ_PH4

8

SS_HA2

9

SCK_SCL

10

MISO_SDA

11

MOSI_HA0

12

IO_G

N

D

13

IO_

V

DD2

14

TDO

15

TDI

16

TMS

17

TCK

18

FST_PC4

48

FSR_PC1

49

SDI1_PC7

50

SDI0_PC6

51

IO_G

N

D2

52

B2005

MMZ1608R102CT

1608

C2098

0.1 B

1005

FROM/TO System Ucom

FROM/TO ADC

!

C

1/8-4/8,6/8-8/8

C

4/8

C

1/8

(D)

(D)

(D)

(D)

(D)

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299