PCM-065/phyCORE-i.MX8X System on Module

L-864e.A1

© PHYTEC America LLC, 2021

38

4

System Memory

The following subsections detail each memory type supported on the phyCORE-i.MX8X.

4.1

DDR4 RAM

The RAM on the phyCORE-i.MX8X is comprised of two 16-bit wide LPDDR4 SDRAM chips for a 32-bit wide

interface providing up to 2GB of SDRAM which can run at up to 1.2 GHz. These chips are connected to the

dedicated DDR processor of the i.MX8X processor. Typically, the DDR4 SDRAM initialization is performed by a

bootloader or operating system following a power-on reset and must not be changed at a later point by any

application code. When writing custom code independent of an operating system or bootloader, SDRAM must

be initialized through the appropriate SDRAM configuration registers on the i.MX8X processor. Refer to

the

i.MX8X Processor Reference Manual

about accessing and configuring these registers. Contact our sales

team for information on the available DDR4 population options:

4.2

EEPROM

The phyCORE-i.MX8X is populated with two nonvolatile 32KB EEPROMs with an I

2

C interface at pad U13/U21.

This memory can be used to store configuration data or other general-purpose data. The devices are accessed

through the PMIC_I2C/MIPI_CSI0_I2C0 on the i.MX8X at address 0x52/0x56.

4.3

eMMC Flash

An eMMC flash device is populated at U4 as a programmable nonvolatile storage. The eMMC flash is connected

to the EMMC0 8-bit interface of the i.MX8X which supports eMMC 5.1.

signals at the U4 eMMC. Contact our sales team for information on the available eMMC population

options:

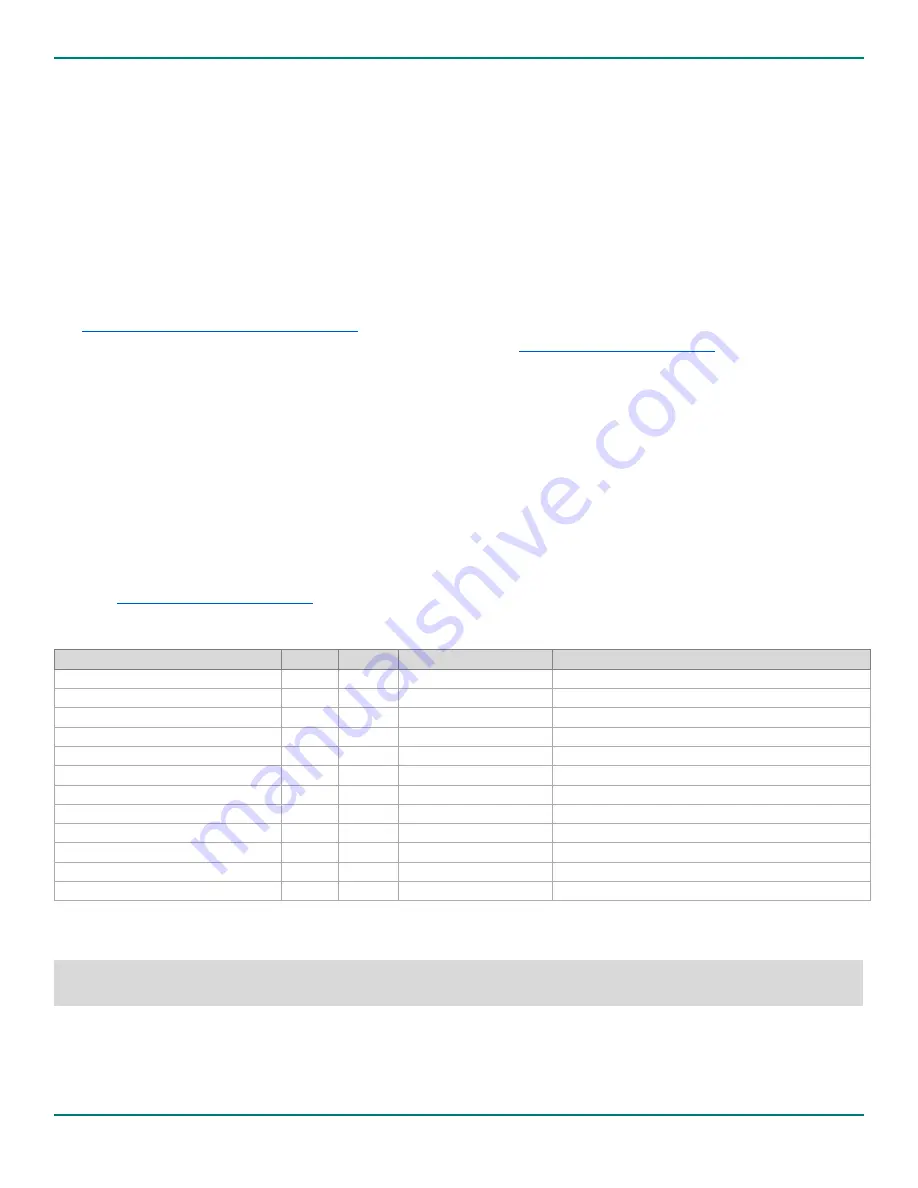

Table 14. eMMC Signal Connections to the Processor

SOM Signal

Type

Level

Processor Ball

Description

EMMC_DATA0/NAND_DATA00

I/O

1.8V

J10

C21

EMMC0 Data 0

EMMC_DATA1/NAND_DATA01

I/O

1.8V

J10

A21

EMMC0 Data 1

EMMC_DATA2/NAND_DATA02

I/O

1.8V

J10

E21

EMMC0 Data 2

EMMC_DATA3/NAND_DATA03

I/O

1.8V

J10

H20

EMMC0 Data 3

EMMC_DATA4/NAND_DATA04

I/O

1.8V

J10

B22

EMMC0 Data 4

EMMC_DATA5/NAND_DATA05

I/O

1.8V

J10

G21

EMMC0 Data 5

EMMC_DATA6/NAND_DATA06

I/O

1.8V

J10

A23

EMMC0 Data 6

EMMC_DATA7/NAND_DATA07

I/O

1.8V

J10

D22

EMMC0 Data 7

EMMC_CMD/NAND_DQS

I/O

1.8V

J10

D20

EMMC0 Command

EMMC_CLK/NAND_READY_B

O

1.8V

J10

G19

EMMC0 Clock

EMMC_STROBE/NAND_CLE

I

1.8V

J10

F22

EMMC0 Data Strobe

EMMC0_RESET_B/NAND_WP_B

O

1.8V

J10

H22

EMMC0 Reset

J10

:

The voltage level for these signals are configurable between 1.8V or 3.3V via jumper J10. In general J10 is set at the factory and should not be

adjusted. The default voltage level is listed here, but always check the actual jumper setting for the applicable SOM configuration. Refer to the

section for details

CAUTION:

eMMC and NAND cannot be populated at the same time.