52

TCM2.0E LA

7.

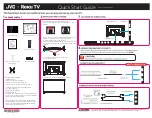

Circuit Diagrams and PWB Layouts

SSB v2: DVBT/ CI Decoder

GND

GND/ADJ

OUT

VIN

4

T

T

GPIO0

GPIO1

GPIO2

GPIO

3

VCC

33

T0CLK_I_

T0

S

YNC_I_

T0VALID_I_

T0DATA0_I_

GND

33

T0DATA1_I_

T0DATA2_I_

T0DATA

3

_I_

T0DATA4_I_

T0DATA5_I_

T0DATA6_I_

T0DATA7_I_

VCC1

8

D

3

D4

D5

D6

D7

GND1

8

CE1#

A10

OE#

A11

A9

A

8

A1

3

A14

GPIO4

GPIO5

GPIO6

VCC

33

_1

WE#

READY

A16

A15

A12

A7

A6

A5

GND

33

_1

A4

A

3

A2

A1

A0

D0

D1

VCC

33

_2

D2

WP

CD1#

D11

D12

D1

3

D14

GND

33

_2

D15

CE2#

V

S

1#

GPIO7

GPIO

8

GPIO9

VCC

33

_

3

IORD#

IOWR#

A17

A1

8

A19

A20

A21

GND

33

_

3

A22

A2

3

A24

A25

V

S

2#

RE

S

ET

VCC1

8

_1

WAIT#

INPACK#

REG#

BVD2

BVD1

D

8

GND1

8

_1

D9

D10

CD2#

GPIO10

GPIO11

GPIO12

CI_CEB

CI_WEB

CI_DATA7

CI_DATA6

VCC

33

_4

CI_DATA5

CI_DATA4

CI_DATA

3

CI_DATA2

CI_DATA1

CI_DATA0

GND

33

_4

CI_CLE

CI_RB

CI_INT

CI_OEB

RE

S

ETB

XTALI

XTALO

AVDD

33

_XTAL

AV

SS33

_XTAL

AVDD1

8

_PLL

AV

SS

1

8

_PLL

VCC

33

_5

T

S

_VALIDO

T

S

_CKO

T

S

_DATAO

T

S

_

S

YNCO

GND

33

_5

GPIO1

3

GPIO14

CI_ALE

VOUT

VIN

EN/EN#

GND

FLG

A

3

2

1

F

E

D

C

B

8

7

6

5

5

4

3

2

1

F

E

D

C

B

A

4

6

7

8

CLO

S

E TO MT

8

295

1.

8

V: 0.2W

(100mA)

3

.

3

V: 0.2W (60mA)

CLO

S

E TO MT

8

295

CLO

S

E TO CI CONNECTOR

CLO

S

E TO CI CONNECTOR

CLO

S

E TO MT

8

295

CLO

S

E TO MT

8

295

CLO

S

E TO MT

8

295

CI_VCC

CI_VPP

CI_IOWR##

C54

8

0.1U

R52

8

10K

R527

0R

C55

8

1U

5

4

3

2

1

U50

3

RT9711

CI_VCC_EN

C547

0.1U

C550

100U

6V

3

L507

3

0R

L509

3

0R

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

16

17

1

8

15

24

26

2

8

3

0

3

2

22

3

5

3

7

3

9

41

44

46

4

8

50

19

20

21

33

5

3

55

57

59

62

64

66

69

4

3

71

7

3

75

7

8

8

0

83

8

5

52

8

7

8

9

2

3

25

27

29

3

1

76

3

4

3

6

38

91

92

9

3

6

8

40

42

45

47

49

51

54

60

56

5

8

61

6

3

65

67

8

2

70

72

74

77

79

8

1

90

8

4

8

6

88

11

8

119

120

94

96

9

8

99

97

100

101

102

95

115

116

104

105

106

114

117

107

110

109

10

8

111

112

11

3

121

122

12

3

124

125

126

127

12

8

10

3

U501

MT

8

295

10P

C567

10P

C561

CI_IOWR#

CI_IORD#

L511

120R

R54

8

NC

CI_RE

S

ET#

R540

33

R

33

R

R5

3

9

R5

38

33

R

T

S

_CKO

CI_CE1##

CI_OE##

CI_WE##

CI_WE##

CI_IOWR##

R5

3

2

NC\0R

R5

33

100R

CI_OUTCLK

CI_V

S

2#

CI_IOWR#

CI_IORD##

CI_IORD#

CI_WE#

CI_OE##

CI_OE#

CI_CE1##

CI_CE1#

R552

100R

R55

3

100R

R551

100R

R549

100R

DV

33

R547

4K7

CI_OEB

R512

10K

R514

4K7

CI_RB

R546

4K7

OPWM2

OPWM1

R525

NC

C559

0.1U

C560

0.1U

C5

38

0.1U

R511

4K7

GND

YPBPR_

S

W_IN

CI_POWE#

T

S

0INDATA7

HDMIED_WP

CI_GPIO0

CI_VPP5_EN

CI_VPP

33

_EN

CI_V

S

1#

CI_IN

S

YNC

CI_INDATA0

HDMI_

S

EL

R519

NC\10K

R517

NC\10K

5V-TUNER-INPUT

5V-TUNER-ON/OF

5

1

2

3

4

6

7

8

9

10

11

1

3

14

15

12

22

21

20

19

1

8

17

16

3

4

33

3

2

3

1

3

0

29

2

8

27

26

25

24

2

3

67

66

65

64

6

3

62

61

60

59

5

8

57

56

55

54

5

3

52

51

50

49

4

8

47

46

45

44

4

3

41

40

3

9

38

3

7

3

6

3

5

6

8

42

P500

R5

3

1

NC/0R

C554

1U

C552

1U

C551

1U

6V

3

47U

C556

C557

47U

6V

3

1U

C1

C541

0.1U

C544

0.1U

C5

3

0

10P

L50

8

600R

L505

600R

L504

600R

CI_VCC

R515

100R

CI_DV

33

Z502

Z501

X501

27M

R521

10K

1

2

3

4

U500

LD1117

S

1

8

CI_IOI

S

16#

CI_INPACK#

CI_DV

33

DV

33

CI_DV1

8

CI_VPP

CI_VCC

CI_DV

33

CI_AV1

8

CI_DV1

8

CI_DV1

8

CI_DV

33

CI_AV

33

CI_DV

33

CI_IOI

S

16#

CI_INPACK#

CI_IREQ#

+5V

+5V

+5V

CI_VCC

CI_VCC

CI_VCC

CI_VCC

CI_VCC

CI_VPP

+5V

C546

0.1U

C545

0.1U

C542

0.1U

C54

3

0.1U

C540

0.1U

C5

3

6

0.1U

C5

3

7

0.1U

C5

3

4

0.1U

C5

3

5

0.1U

C5

3

9

0.1U

C5

3

2

0.1U

C5

3

1

0.1U

C5

33

0.1U

R524

10K

R52

3

10K

R520

10K

R51

8

10K

R516

10K

R522

10K

CI_GPIO1

CI_DV

33

T

S

0INVALID

T

S

0INDATA0

GND

CI_CD1#

CI_INCLK

R51

3

0R

R510

4K7

T

S

_VALIDO

T

S

_DATAO

T

S

_

S

YNCO

RE

S

ET_N

CI_GPIO14

R509

1M

C52

8

27P

C529

27P

CI_XTALO

GND

GND

GND

GND

GND

GND

GND

CI_DV

33

CI_DV

33

CI_DV

33

CI_DV

33

CI_DV

33

CI_INDATA7

CI_OUTCLK

CI_OUTDATA7

CI_OUTDATA2

CI_INDATA5

CI_REG#

CI_OUTDATA1

CI_CD1#

CI_V

S

1#

CI_OUT

S

YNC

CI_DV1

8

CI_DV1

8

CI_OUTDATA5

CI_INDATA1

CI_WAIT#

CI_WAIT#

CI_CE2#

CI_OUTDATA6

CI_OUTDATA0

CI_INDATA2

CI_RE

S

ET

CI_VCC_EN

CI_OUTDATA

3

CI_IREQ#

CI_AV

33

CI_IOI

S

16#

CI_INDATA

3

CI_AV1

8

CI_OUTVALID

CI_INDATA6

CI_CD2#

CI_CD2#

CI_INDATA4

CI_OUTDATA4

CI_INPACK#

CI_IORD##

CI_PDD

3

CI_PDD7

CI_D7

T

S

0INCLK

CI_D6

T

S

0INDATA5

CI_ALE

CI_PDD6

CI_A0

CI_PDD2

CI_INDATA7

CI_D

3

CI_V

S

2#

CI_OUTDATA7

CI_A7

CI_OUTDATA2

CI_INDATA5

CI_A9

CI_REG#

CI_OUTDATA1

CI_D4

CI_A

3

CI_A1

3

CI_V

S

1#

CI_IN

S

YNC

T

S

0INDATA1

CI_OUT

S

YNC

CI_D0

CI_OUTDATA5

CI_A2

CI_INDATA1

CI_A5

CI_INT

CI_A10

CI_A12

CI_XTALI

CI_WAIT#

T

S

0INDATA2

CI_INDATA0

CI_CE2#

T

S

0INDATA6

CI_OUTDATA6

CI_OUTDATA0

CI_INDATA2

CI_RE

S

ET

CI_INVALID

T

S

0INDATA

3

CI_OUTDATA

3

T

S

0INDATA4

CI_A

8

CI_A4

CI_A1

T

S

0IN

S

YNC

CI_A11

CI_PDD5

CI_INDATA

3

CI_D1

CI_A6

CI_CLE

CI_OUTVALID

CI_D5

CI_INDATA6

CI_D2

CI_INDATA4

CI_PDD4

CI_OUTDATA4

CI_A14

CI_A6

CI_A5

CI_A4

CI_A

3

CI_A2

CI_A1

CI_A0

CI_D0

CI_D1

CI_D2

CI_IREQ#

CI_INVALID

CI_A12

CI_A7

CI_A

8

CI_WE#

CI_A14

CI_A1

3

CI_A9

CI_A11

CI_OE#

CI_A10

CI_CE1#

CI_D7

CI_D5

CI_D4

CI_D

3

CI_D6

CI_T

S

_

S

YNCO

CI_T

S

_DATAO

CI_T

S

_VALIDO

HPDIN

CI_CD1#

CI_CD2#

CI_POCE1#

MTK_IC_RE

S

ET

CI_GPIO1

CI_GPIO0

CI_INCLK

10P

C562

10P

C565

10P

C566

10P

C564

10P

C56

3

R550

100R

CI_V

S

2#

CI_T

S

_CKO

33

R

R541

PWRDN_EN

1795

3

_525_090

33

0.ep

s

090

33

1

DVBT-CI-DECODER

B05

B05