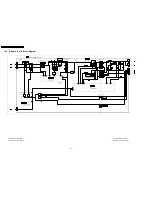

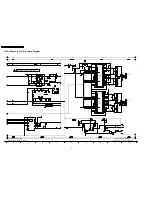

15.2. Main Block Diagram

DH

OSD

25

FULL HD

DH

DH5

D5

25

FPGA

DG

GP5P_1st

(CYCLONE)

DDR

CH0DATA

FAN CONTROL

LINE

CONTROL

S.R.

SUSTAIN

HDMI 3

D36

*Plasma AI

GS09

H264 L/R

POWER SW

W-R

S.R.

S.R.

Vda

Discharge

Control(SC)

ASDIO

C2

28

C3

H264 DECODER

JG10

S.R.

SWITCH

S.R.

LVDS TX

SOS7

PULSE

P5V

RECTIFIER

C25

*H,V Snyc Control

AMP

+15V

SOS6

PA33

DG

P5V

S.R

W-L

MICON

PROCESSOR

64

AMP

S.R.

AUDIO IN

AV SWITCH

D/A

EEPROM

POWER

64

+15V

64

END

STANDBY

S.R

SC2

S.R

GS52

D20

64

POWER LED

DG1

15V

H11

+12V(s)

VOLTAGE

S.R.

G[9:0]

PRO.

SPEAKER

S.R.

R[9:0]

HDMI3 IN

C4

64

ADDRESS

HDMI_SPDIF

VDA_75V

AV3 IN

S.R

AD/HDMI

S.R

Peaks-Lite 2

DG6

S.R

Data Driver

Control

JG19

DTV_SDIN

VOLTAGE

C22

VDA_75V

PLASMA AI PROCESSOR

S.R.

SCAN DRIVE

SENSOR

SD

PULSE

SU

H12

D35

64

64

D25

SS

GH

DG

MAIN

MICOM

D34

FORMAT CONVERTER,

C24

+15V

HDMI

EQ

(VE)

PA32

SD CARD I/F

64

C1

BOOT

ROM

H

SD CARD SLOT

DATA DRIVER(CENTER)

S.R.

STB_PS

VOLTAGE

DATA DRIVER(LEFT)

AUDIO D/A

G

SUSTAIN

JG

DTV

S.R.

S.R.

FILTER

H264

*CLK

Vda

POWER_SOS

RESET

SUSTAIN DRIVE

DATA DRIVER(CENTER)

VDA_75V

S.R.

PROTECTION(SOS)

P

RECTIFIER

S.R

S.R.

PD1-M plus

L

VOLTAGE

WRITE PROTECT

S.R

H6

5V

15V

SS35

DISPEN

DC/DC

3.3V

BOOT

ROM

P5V

+12V

PCLK/NCLK

S.R.

PROCESS

ERASE

POWER SUPPLY

64

SUS

+15V

D

64

64

S1

SOS7

TEMP

REMOTE/LED/KEY SW

P12

SS11

*VD,HD

P_ON/OFF

S.R

S.R

*Sub Filed Processor

Peaks-

PRO

X'tal

C31

SIGNAL

CONTROL

HDMI IN 1

DATA DRIVER(RIGHT)

AUDIO

F_STB+15V

DATA0

B[9:0],HD,VD

SS12

DC/DC

1.8V

SOS8

IIC2

SW

PC IN

S.R

+15V

(UP)

64k

S.R.

S.R.

P5

REMOTE RECEIVER

DG11

VSUS

32Mbit

Flash-ROM

PULSE

STB5V

S.R.

SUSTAIN

AUDIO OUT

(4MByte)

AI SENSOR

64

C51

S.R.

S.R.

FLASH CONTROL

JG08

VOLTAGE

DC/DC

1.2V

SW

128Mbit

DDR

P1.2V

64

D32

C21

S.R.

S.R.

PROM

C35

P25

C44

SS42

35

POWER

S.R

RECTIFIER

P11

DATA DRIVER(LEFT)

L/R

Vda

HDMI_SDIN

S.R

H8

S.R

USB Rx

S.R.

PULSE

S

+15V

P5V

VOLTAGE

DIGITAL

VDA_75V

D33

EQ

+5V

RESET

SOS8

S.R.

*Discharge Control

C6

STB12V

64

C60

DDR2x2

VOLTAGE

DRVRST

*RGB:10bit(or8bit)

PROCESSOR

P9

R,G,B

AVR

CARD

SPEAKER

R

AV TERMINAL

S.R.

RELAY

L/R

STB3.3V

ICEOUT

Vda

S.R.

CONTROL

P2

SC20

CONTROL

C55

Genx4

(DOWN)

CONTROL

SOUND_SOS

PCLK/NCLK

VIDEO

P3.3V

FILTER

USB Tx

V

REG

RESET

FRONT

SQ-R

D5

C41

PROCESS

S-VIDEO IN

STBY5V_M

12V

RECTIFIER

C52

Discharge

Control(SS)

VSUS

H264 SPDIF

R

CLOCK

SOUND

SUSTAIN

VIDEO IN

FACTOR

C54

SC

64

*LVDS receiver

SOS

C42

VCXO

28

P5V

S.R.

SCAN

H51

VSUS

RECTIFIER

BOOT

ROM

Y,C,V

SOS6

SPEAKER

MAIN_L/R

PULSE

SS44

DTV_V

Data Driver

Control

GENERATOR

L

PS_SOS

GS

LVDS format

D31

K1

SQ-L

VDA_75V

L/R

DRIVE

KEY SCAN

SW

P5V

Vda

AC CORD

Vda

DATA DRIVER(RIGHT)

S.R

GH11

GENERATOR

SD

AV3 IN

PA35

[27MHz]

VDA_75V

SCAN OUT

DCLK

FAN

S.R

K

64

VOLTAGE

FAN SOS

NOR

FLASH

C11

S.R

DG52

S.R

P2.5V

D3

NOR

FLASH

HDMI

EQ

VDA

G51

DC/DC CONVERTER

TUNER

DCK

S.R.

SIGNAL

LINE

XRST

DIGITAL

S.R.

Y,Pb,Pr

S.R.

MAIN

SLOT

C61

P10

C5

FPGA

HDMI IN 2

C10

STANDBY

SCAN OUT

DH8

SS34

ANALOG

TUNER

GC3FS

SCART

AV3

SCART

AV1

COMP

SCART

VIDEO

AV2

L/R

L/R

L/R

V,R,G,B

V,R,G,B

V,Y,C

SUB

DC POWER

H3

H2

DG2

PA3

DC/DC

CONVERTER

PA5

PA10

PA DC-DC CONVERTER

POWER SOS

FAN_SOS

FAN

TH-50PY700F/P, PZ700B/E

Main Block Diagram

TH-50PY700F/P, PZ700B/E

Main Block Diagram

TH-50PZ700B / TH-50PZ700E / TH-50PY700F / TH-50PY700P

76

Summary of Contents for Viera TH-50PZ700B

Page 5: ...1 Applicable signals 5 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 23: ...8 2 Lead of Wiring 2 23 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 24: ...8 3 Lead of Wiring 3 24 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 28: ...9 4 No Picture 28 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 40: ...40 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 158: ...16 2 Packing Exploded Views 1 158 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 159: ...16 3 Packing Exploded Views 2 159 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 160: ...16 4 Packing Exploded Views 3 160 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 161: ...16 5 Replacement Parts List Notes 161 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...