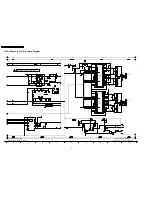

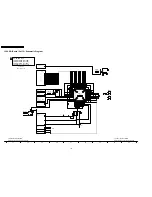

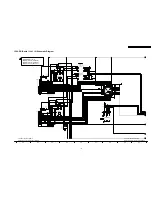

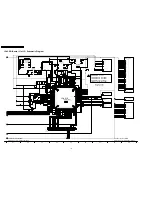

15.28. DG-Board (2 of 3) Block Diagram

SDA2

SCL2

XIRQ2

CH0VAL

MDO4

MDO3

MDO2

CH0DATA

MDO6

CH0CLK

MDO1

CH0PSYNC

MDO5

MDO7

VI1P20

IS0PSYNC

CH0CLK

CH0DATA

CH0PSYNC

CH0VAL

SRCK0

DMIX0

IECOUT0

D

A

UDIO

LRCK0

SCL3

SDA3

SD

A1

SCL3

SD

A3

SCL1

SD

A2

SCL2

MVD

A

CO3

T

O_GC3FS_NEXT

TMS

T

O_BA01

TCK

TRST

FE_XRST

TV_MAIN_ON

FPGA_XRST

CNFIG_DONE

HQ1_XRST

HSOE

LOSCLKIN

VSOE

LOSDHIN

CLK

OE

LOSD

VIN

PEAKS_YM

PEAKS_YS

PEAKS_OSHIN

PEAKS_OSDCK

O

LOSDHIN

VSOE

CLK

OE

HSOE

PEAKS_OSDCK

O

PEAKS_OSHIN

PEAKS_YS

PEAKS_YM

LOSD

VIN

LOSDCLKIN

CLK74SEL

SBI2

SBO0

SBO2

L

VDS_EN

SBI0

SD_LED_ON

V

OUTENB

SLRCK

ADCCK

VI2ENB

AUDCLK

SD_BOOT_STS

PANEL_STATUS

PANEL_SOS

PANEL_MUTE

XRST

XIRQ3

RXD0

FORMAT-EDGE

TXD0

PRO_SDBOOT

PRO_XRST

POWER_DET

SCL0

SD

A0

MAIN_ON

VI1CK

OUT

VI1CLK

VI1ENB

VI1VSYNC

VI1HSYNC

VI2CLK

VI2HSYNC

VI2VSYNC

DTV9V

SUB1.2V

SUB3.3V

SUB1.8V

SUB5V

SUB3.3V

SUB5V

SUB3.3V

SUB3.3V

SUB5V

SUB3.3V

SUB5V

LRCK0

IECOUT0

SRCK0

D

A

UDIO

DMIX0

SUB3.3V

SCL1

SD

A0

SD

A2

SCL0

SD

A3

SD

A1

SCL2

SCL3

TMS

TDI

TRST

TCK

TDO

CK27D

CLK74

VC27

CK27

XIRQ3

XIRQ2

XECS6

XRST

X8301

Q8402

Q8401

SUB3.3V

SBO2

SBI0

SBI2

SBO0

V

OUTENB

RMCO

DSRCK

VI2P21

VI2P10

VI2ENB

ADCCK

SLRCK

AUDCLK

ADIN

D8850

Q8911

Q8913

Q8912

1

RESET

2

PEAKS LITE2 RESET

Analog

Video

I/F

CLOCK GEN

512M DDR

IC8002,03

SUB1.8V

74M

CLOCK GENE.

27M

4

9

7

S2

14

VIN

SUB3.3V

IC8004

IF_AGC

IFD1

IFD2

SDA

DVB TUNER

BM

BB

SCL

TU8301

15

16

14

17

18

11

3

31

30

42

35

36

/VIN

VIN

AGC1

CLK2

DATA2

+1.8V

1

8

IC8302

+1.8V

5

DATA1

4

CLK1

6

/IRQ

9

RESET

61

58

57

56

53

52

51

50

49

48

47

IC8301

FRONT END

IC8404,05

TS BUFFER

DATA0-7

45

61

10

50

30

41

56

21

59

51

IREQ#

29

6

ENINA,CLKINA

57

MDO3-MDO7

36

VCC

JK8401

MDO0-MDO2

RESET

7

19

A0~A14

16

64

CE1#

CD1#,CD2#

58

MISTRT

52

(COMMON

9

OE#,WE#

MCLK0,WAIT#

46

REG#

18

INTERFACE)

53

IORD#,IOWR#

66

37

CI SLOT

2

D0~D7

Vpp1,Vpp2

63

67

ENOUT,PKTRTOUT

62

15

MDI0~MDI7

PKTSTINA

8

44

20

32

47

17

14

MIBAL,MCLKI

BUFFER

IC8409

IC8402

BUFFER

IC8406,IC8407

EA1-EA15

BUFFER

ADDRESS

ED0-ED7

DATA(8bit)

IC8401

CONTROL

CONTROL

DATA0-7

BUFFER

IC8408

DATA BUFFER

4

FAULT

1

SUB 5V

VIN

CARD 5V

VOUT

3

IC8403

6

EN

CI_POWER_ON

CI_OCP

POD

CI

I/F

PEAKS_Lite 2

IC8001

CI PARALLEL

TS

IC8621,22

D-LATCH

NOR FLASH

IC8554

DATA0-7

ExBUS

TUNER SERIAL TS

SPDATA

Comp

.

with A

UDIO DESCRIPTION D

A

T

A

MAIN A

UDIO D

A

T

A

DIGIT

AL A

UDIO

COMMON LR/SR CLK

for PHO

T

O OUT

AUDIO IF

CPU BUS I/F

POD,CI I/F

IC8601

EEPROM

8

7

6

5

EEPROM_WP

VCC

WP

SCL

SDA

IIC I/F

COFDM DEMODULATOR

JTAG

JTAG

HDMI_IRQ

FE_IRQ

FE_XRST

I2C

I2C

I2C

VDD

PZ700B/E ONLY

DG

DIGITAL SIGNAL PROCESSOR

16

15

14

17

11

13

3

1

2

5

Sub Video

Input

4

Y0-9

R0-4

UV0-7,Y0-7

IC5660

MOSTRT

MOVAL

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MOCLK

23

24

20.48MHz

XTT

XT0

CHDI0-CHDI7

CHVAL,CHSYNC,CHCLK,SMTCMD0,SMTSEL0,XPDWT,SMTCLK0

REG,WE,IOWR,IORD,OE,CE1

ED0-ED15

EA8-EA23

ED0-ED15

EA1-EA23

(128/256Mbit)

SUB 3.3V

SUB 5V

SBO1

XRTS0

ED0-ED15/EA8-EA23

EA0-EA7,EA24

CI_XRST(VI2P20)

VDD

CVDD

37

49

GOE9

TMS

,TRST

MAIN3.3V

VSOE

SCL0

107

LOSDHIN

57

36

LOSD

VIN

PEAKS_YM

LOSD0

LOSD15

38

TDO(T

O SC)

CLK

OE

84

77

RO

E

2

95

R

OE2-R

OE9

R

OE9

HQ1_XRST

50

TCK

GOE2-GOE9

51

BOE2-BOE9

104

TDI(T

O HQ1)

SUB 5V

105

MAIN 3.3V

TV_MAIN_ON

DG25

86

59

60

102

56

34

58

TRST

53

PEAKS_OSDCK

O

32

12

TDI,TDO

10

40

GOE2

11

TO

DH25

FPGA_RST

42

63

52

65

LOSDCLKIN

35

47

7

MAIN 3.3V

CNFIG_DONE

OSD_FLA

G

62

PEAKS_YS

TMS

,TCK

SD

A0

43

14

HSOE

2

30

1

64

JT

A

G

PEAKS_OSHIN

74

CFG_JT

A

G

BOE2

93

SUB9V

SUB 9V

SUB5V

SUB 9V

75

3

BOE9

SCL0

SD

A0

I2C

(VI2P9)LOSD_H_I

(VI2P8)LOSD_CLK_I

(VI2P7)LOSD_V_I

(VI2P6)LOSDOUT_YM

(VI2P5)LOSDOUT_YS

(VI2P2)LOSDOUT_CLK

O

(VI2P3)LOSDOUT_H_O

HQ1L VIDEO

MVCLK

MHSYNC

GOE9

MVSYNC

BOE2-BOE9

BOE2

R

OE2-R

OE9

GOE2-GOE9

BOE9

LOSDO0-LOSDO15

(V

OP22)

(V

OP29)

(V

OP12)

(V

OP19)

(V

OP2)

(V

OP9)

RO

E

9

GOE2

RO

E

2

LOSDOUT0

LOSDOUT15

3

8

10

13

SDCMD

11

SDDTC

SDD

A

T3

7

9

SDD

A

T0

SD_LED_ON

SD

WP

SDD

A

T2

SDD

A

T1

5

3.3V

SDCLK

DG52

1

12

ISOD

A

T

A

14

SD

WP

SD

A

T3

SD CARD

SDCMD

SD

A

T1

SD CARD I/F

SDCD

SD

A

T2

SDCLK

SD

A

T0

6

L

VDS_EN

OSD_FLA

G

ISOD

A

T

A

LOSD OUT (HQ1)

SERIAL I/F

VMUTE

SDBOOT

ETHER_IRQ

RSV2(SDRAMCHK2)

RSV3(SDRAM_CHK1)

RSV4

RSV1(SD_ERROR)

PANEL_STATUS

PANEL_SOS

COMMON POR

T .etc

PRO-XRST

FORMAT-EDGE

PRO-SDBOOT

TXDO

RXDO

POWER_DET

ISOVAL

IS1PSYNC

VI1P21

IS1VAL

ISOCLK

VI1P10

12

MVD

A

C03

UV0-9

VI1P2-9

VI1P12-19

VI1P22-29

CLKIA(VI1CLK)

CLK

O

A(VI1CK

OUT)

VSIA(VI1VSYNC)

HSIA(VI1HSYNC)

VI1ENB

Y0-7

UV0-7

VI2HSYNC

VI2VSYNC

VI2CK

OUT

B Port

Address

VI2CK

OUT

VI2HSYNC

VI2VSYNC

VI2P4

VI2P22-29

VI2P12-19

EA08-15

EA24

EA16-23

ADV7493

CH,IS IF

TH-50PY700F/P, PZ700B/E

DG-Board (2 of 3) Block Diagram

TH-50PY700F/P, PZ700B/E

DG-Board (2 of 3) Block Diagram

TH-50PZ700B / TH-50PZ700E / TH-50PY700F / TH-50PY700P

102

Summary of Contents for Viera TH-50PZ700B

Page 5: ...1 Applicable signals 5 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 23: ...8 2 Lead of Wiring 2 23 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 24: ...8 3 Lead of Wiring 3 24 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 28: ...9 4 No Picture 28 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 40: ...40 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 158: ...16 2 Packing Exploded Views 1 158 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 159: ...16 3 Packing Exploded Views 2 159 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 160: ...16 4 Packing Exploded Views 3 160 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Page 161: ...16 5 Replacement Parts List Notes 161 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...