User’s Manual

93

7.8 Watchdog Timer

The watchdog timer is a 17-bit counter. In normal operation it is driven by the 32.768 kHz

clock. When the watchdog timer reaches any of several values corresponding to a delay of

from 0.25 to 2 seconds, it “times out.” When it times out, it emits a 1-clock pulse from the

watchdog output pin and it resets the processor via an internal circuit. To prevent this tim-

eout, the program must “hit” the watchdog timer before it times out. The hit is accom-

plished by storing a code in WDTCR. Note that although a watchdog timeout resets the

processor, it does not reset the timeout period stored in the WDTCR. This was done inten-

tionally because an application may require the initialization of the processor resulting

from the watchdog timeout to be based on a specific timeout period that is different from

that of the reset initialization.

The watchdog timer may be disabled by storing a special code in the WDTTR register.

Normally this should not be done unless an external watchdog device is used. The purpose

of the watchdog is to unhang the processor from an endless loop caused by a software

crash or a hardware upset.

It is important to use extreme care in writing software to hit the watchdog timer (or to turn

off the watchdog timer). The programmer should not sprinkle instructions to hit the watch-

dog timer throughout his program because such instructions can become part of an endless

loop if the program crashes and thus disable the recovery ability given by having a watch-

dog.

The following is a suggested method for hitting the watchdog. An array of bytes is set up

in RAM. Each of these bytes is a virtual watchdog. To hit a virtual watchdog, a number is

stored in a byte. Every virtual watchdog is counted down by an interrupt routine driven by

a periodic interrupt. This can happen every 10 ms. If none of the virtual watchdogs has

counted down to zero, the interrupt routine hits the hardware watchdog. If any have

counted down to zero, the interrupt routine disables interrupts, and then enters an endless

loop waiting for the reset. Hits of the virtual watchdogs are placed in the user’s program at

“must exercise” locations.

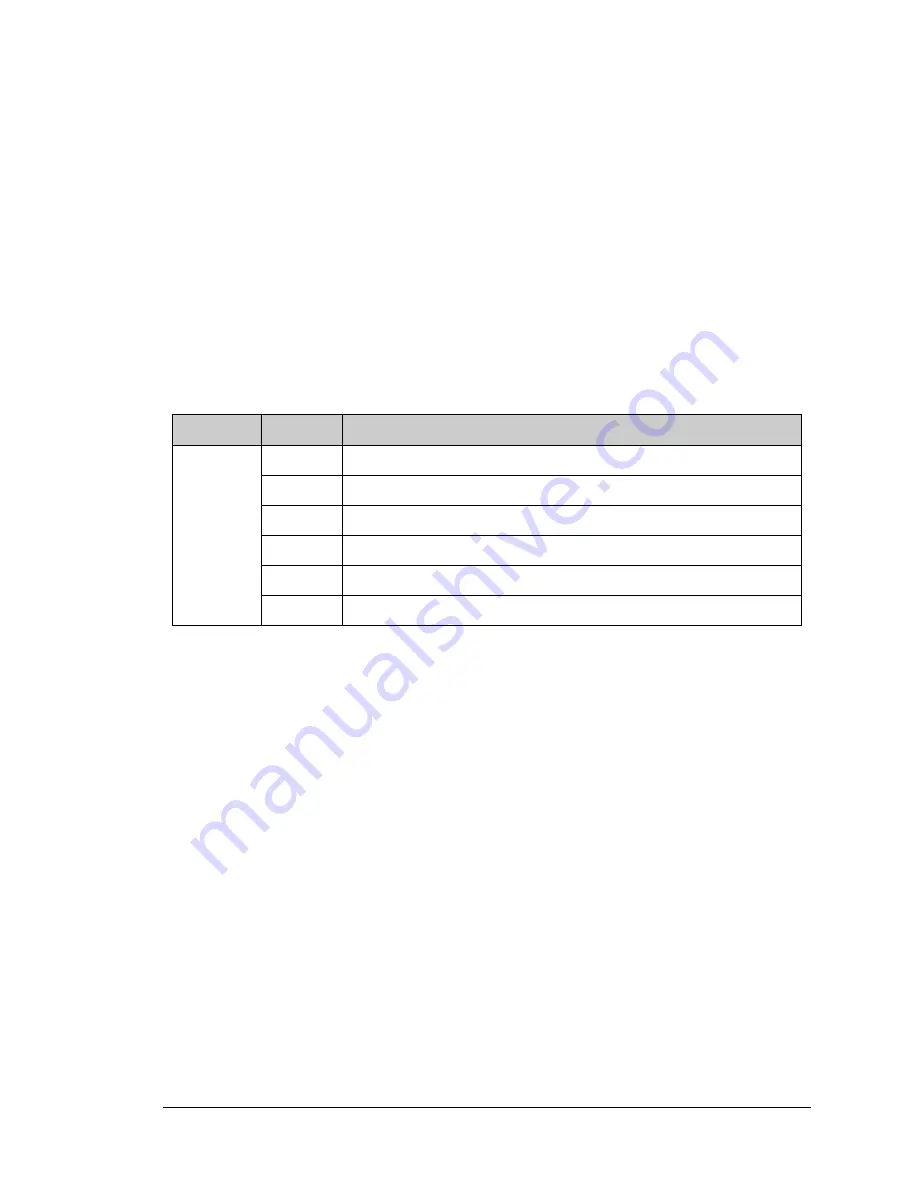

Table 7-12. Watchdog Timer Control Register (WDTCR adr = 0x08)

Bit(s)

Value

Description

7:0

0x5A

Restart (hit) the watchdog timer, with a 2-second timeout period.

0x57

Restart (hit) the watchdog timer, with a 1-second timeout period.

0x59

Restart (hit) the watchdog timer, with a 500 ms timeout period.

0x53

Restart (hit) the watchdog timer, with a 250 ms timeout period.

0x5F

Restart the secondary watchdog timer (starting with Rabbit 3000A chip).

other

No effect on watchdog timer.

Summary of Contents for Rabbit 2000

Page 2: ...Rabbit 3000 Microprocessor User s Manual 019 0108 040731 O ...

Page 9: ...Rabbit 3000 Microprocessor ...

Page 29: ...20 Rabbit 3000 Microprocessor ...

Page 64: ...User s Manual 55 5 PIN ASSIGNMENTS AND FUNCTIONS ...

Page 79: ...70 Rabbit 3000 Microprocessor ...

Page 80: ...User s Manual 71 6 RABBIT INTERNAL I O REGISTERS ...

Page 123: ...114 Rabbit 3000 Microprocessor ...

Page 137: ...128 Rabbit 3000 Microprocessor ...

Page 157: ...148 Rabbit 3000 Microprocessor ...

Page 207: ...198 Rabbit 3000 Microprocessor ...

Page 249: ...240 Rabbit 3000 Microprocessor ...

Page 255: ...246 Rabbit 3000 Microprocessor ...

Page 277: ...268 Rabbit 3000 Microprocessor ...

Page 343: ...334 Rabbit 3000 Microprocessor ...

Page 345: ......