User’s Manual

181

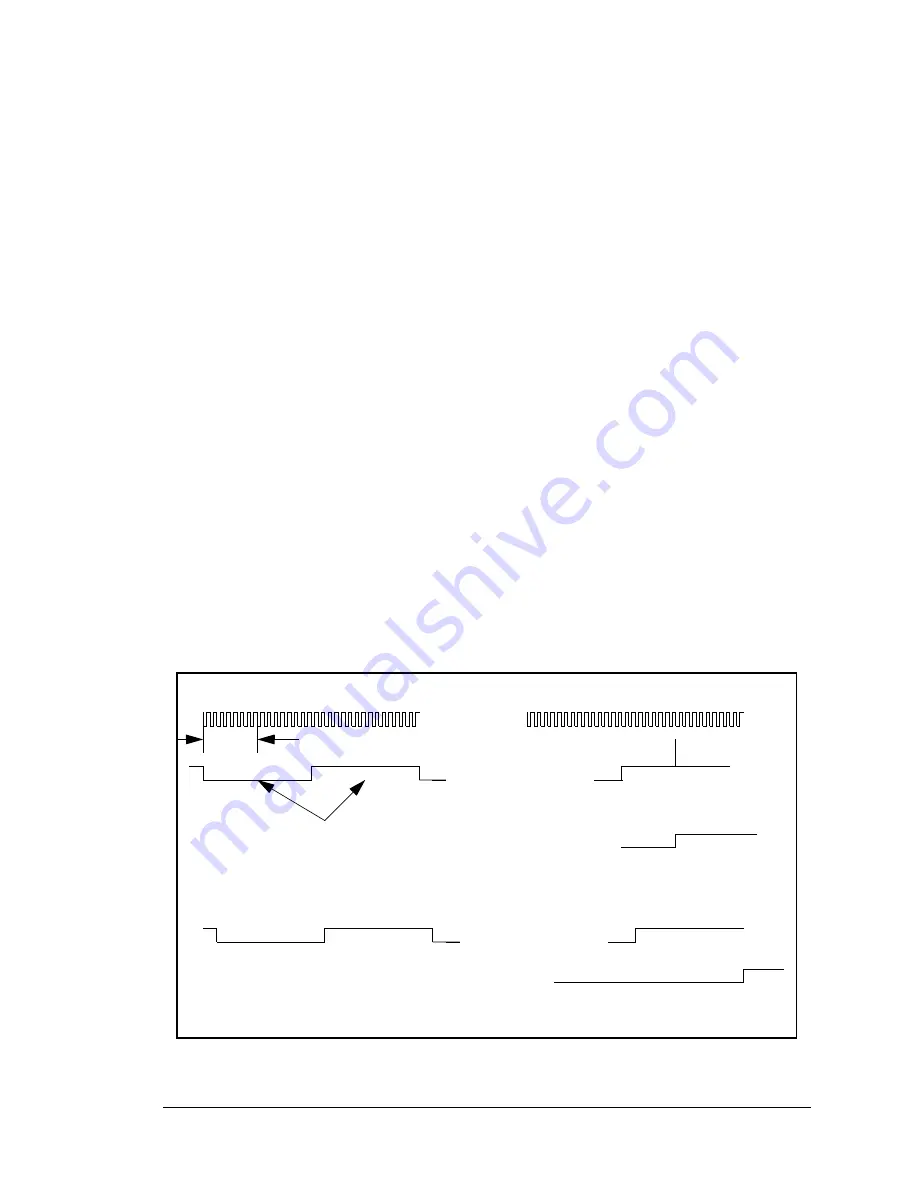

12.5 Receive Serial Data Timing

When the receiver is ready to receive data, a falling edge indicates that a start bit must be

detected. The falling edge is detected as a different Rx input between two different clocks,

the clock being 8x or 16x the baud rate. Once the start bit has been detected, data bits are

sampled at the middle of each data bit and are shifted into the receive shift register. After

7 or 8 data bits have been received, the next bit will be either a 9th (8th) address bit, or a

stop bit will be sampled. If the Rx line is low, it is an address bit and the address bit

received bit in the status register will be enabled. If an address bit is detected, the receiver

will attempt to sample the stop bit. If the line is high when sampled, it is a stop bit and a

new scan for a new start bit will begin after the sample point. At the same time, the data

bits are transferred into the receive data register and an interrupt, if enabled, is requested.

On receive, an interrupt is requested when the receiver data register has data. This hap-

pens when data bits are transferred from the receive shift register to the data register. This

also sets bit 7 of the status register. The interrupt request and bit 7 are cleared when the

data register is read.

An interrupt is requested if bit 7 is high. The interrupt is requested on the edge of the

transmitter data register becoming empty or the transmitter shift register becoming empty.

The transmitter interrupt is cleared by writing to the status register or to the data register.

On receive, the scan for the next start bit starts immediately after the stop bit is detected.

The stop bit is normally detected at a sample clock that nominally occurs in the center of

the stop bit. If there is a 9th (8th) address bit, the stop bit follows that bit.

The serial clock can be configured to be either 16× the data rate or 8× the data rate.

Figure 12-4. Serial Port Synchronization

start bit

8 clocks

stop bit

Receiver Data

Ready Bit

sampling

point

Serial Port

Input Clock

Asynchronous Receive

Asynchronous Transmit

Transmitter Data Reg Full

Summary of Contents for Rabbit 2000

Page 2: ...Rabbit 3000 Microprocessor User s Manual 019 0108 040731 O ...

Page 9: ...Rabbit 3000 Microprocessor ...

Page 29: ...20 Rabbit 3000 Microprocessor ...

Page 64: ...User s Manual 55 5 PIN ASSIGNMENTS AND FUNCTIONS ...

Page 79: ...70 Rabbit 3000 Microprocessor ...

Page 80: ...User s Manual 71 6 RABBIT INTERNAL I O REGISTERS ...

Page 123: ...114 Rabbit 3000 Microprocessor ...

Page 137: ...128 Rabbit 3000 Microprocessor ...

Page 157: ...148 Rabbit 3000 Microprocessor ...

Page 207: ...198 Rabbit 3000 Microprocessor ...

Page 249: ...240 Rabbit 3000 Microprocessor ...

Page 255: ...246 Rabbit 3000 Microprocessor ...

Page 277: ...268 Rabbit 3000 Microprocessor ...

Page 343: ...334 Rabbit 3000 Microprocessor ...

Page 345: ......