Application Note

15 of 23

V 1.1

2020-11-09

CoolGaN™ 600 V half-bridge evaluation platform featuring GaN

EiceDRIVER™

Setup and use

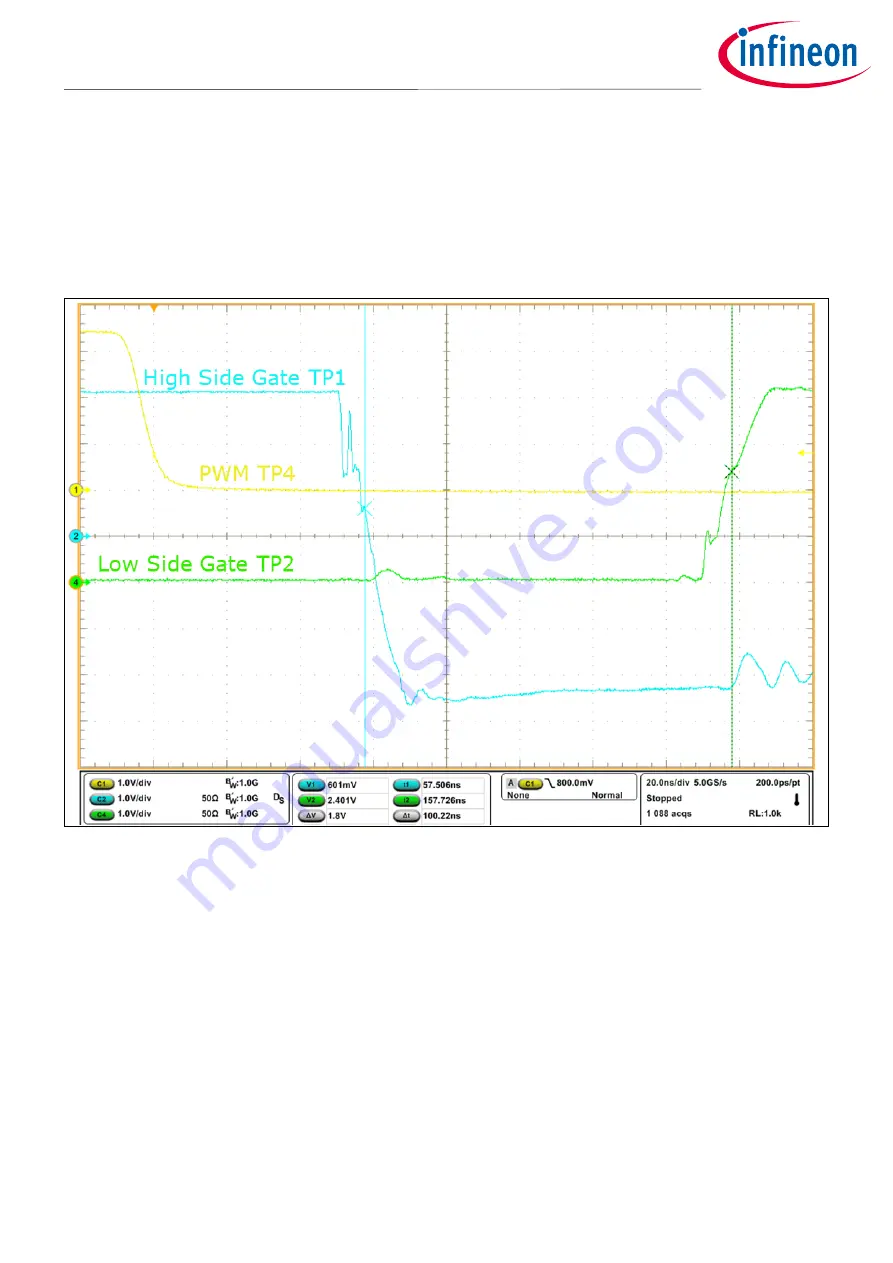

Apply power to the board and trigger on the rising edge of TP4. You should have a signal that looks similar to

. The cursors assume that turn-off is complete when TP2 crosses 0 V, and turn-on is assumed to begin

when TP1 reaches about 2.5 V. Adjust R11 (trimpot) to achieve the desired deadtime (factory preset is 100 ns).

For the falling edge, set the scope trigger for the negative edge of TP4, and you should see a waveform similar

to

. Adjust trimpot R21 to dial-in the deadtime to the desired value on the falling edge of PWM.

Normally the rising and falling edge deadtimes are set to the same value. Turning the trimpots clockwise

increases the deadtime.

Figure 13

Measuring deadtime on the falling-edge of PWM

4.7

Test inductor recommendation

For best results, it is recommended that a good high-frequency capable inductor is used for testing. We

recommend a Micrometals T200-2B toroidal core, with 34 turns of 14 gauge HPN enameled copper magnet wire

in a single-layer. This provides a very linear, low-loss 25 µH inductor with a self-resonant frequency >20 MHz

and a high saturation current, well beyond the rating of the 70 mΩ GaN peak current rating. While this may not

provide the most space-efficient inductor, it will not “color” the measurement results. Lower performance

inductors may have high self-capacitance and multiple resonaces that can mask or confuse the performance

measuremet of the GaN half-bridge.