21

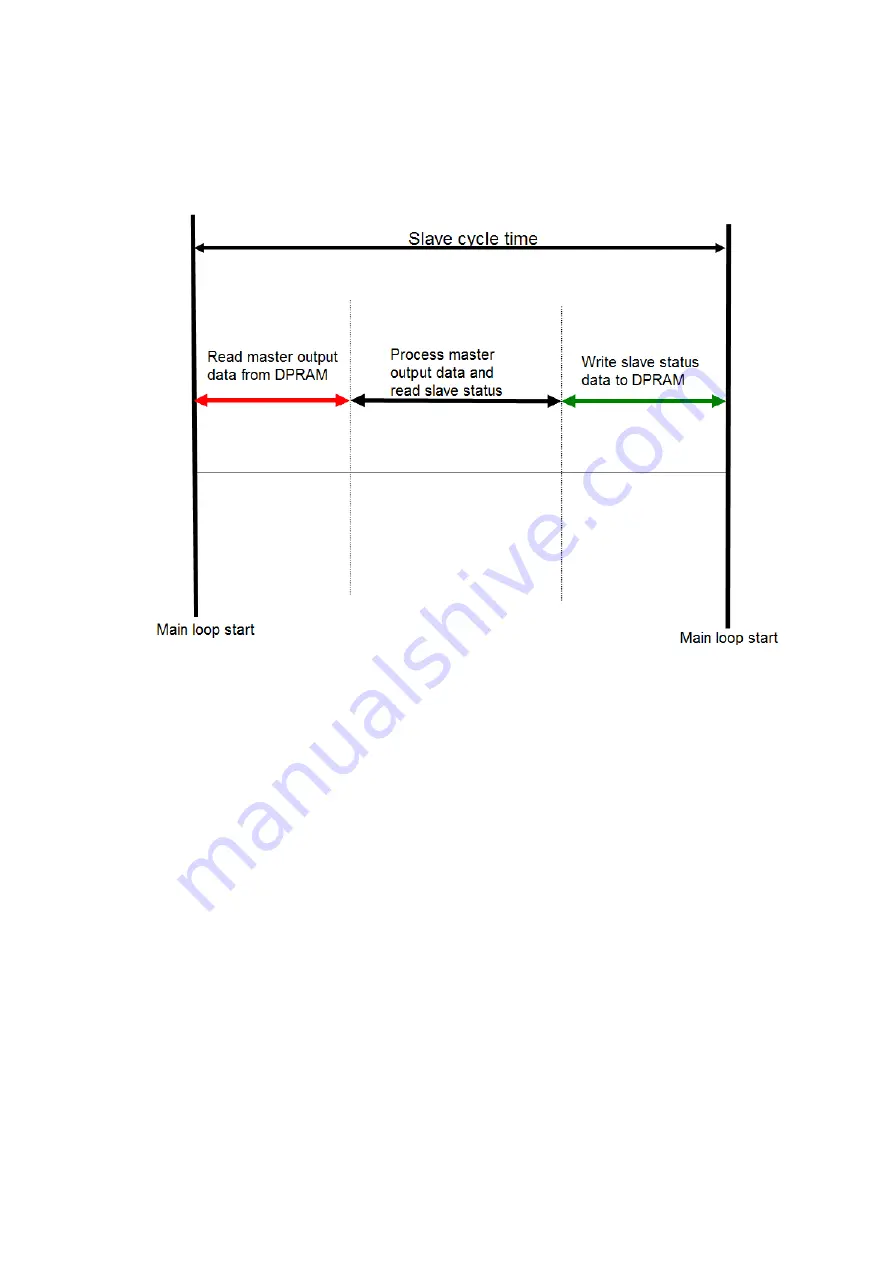

The following diagram shows the process timing of the slave in Free Run mode in detail:

Figure 5: Slave processing sequence in Free-run mode

The slave firmware checks in each cycle time the memory of the EtherCAT slave chip

(ESC) whether new output data has been received from the master. Newly received

data will be processed and the motion path will be calculated. In the next step

motion and digital input status are being read from motion chip. In the final step the

read status are being written to the DPRAM, so that the master can retrieve the data

ESC DPRAM in the next cycle time.

3.3.2

Distributed Clocks (DC Mode)

DC clock synchronization enables all EtherCAT devices (master and slaves) to share

the same EtherCAT system time. The EtherCAT slaves in the network can be

synchronized to each other. This enables the master to simultaneously set the output

(e.g. digital output, pulse output) or to synchronously read inputs (e.g. digital input,

encoder counter) of different slaves in the EtherCAT network.

Summary of Contents for ECAT-2094P

Page 1: ...ECAT 2094P EtherCAT 4 Axis Pulse Output Module User Manual Version 1 0...

Page 10: ...10 2 2 Alias Rotary Swtich The Alias range is 0x00 0xFF...

Page 15: ...15 2 5 Stepper Motor Wiring...

Page 17: ...17 Figure 2 Open collector wiring diagram...

Page 24: ...24 is the total execution time of all slave application related operations...

Page 71: ...71 Method35 37 The home detection position is the current position...