GDV 130…

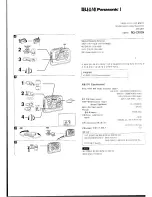

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GDV 130…

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GRUNDIG Service

2 - 14

GRUNDIG Service

2 - 15

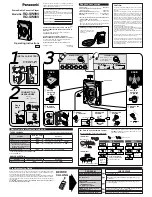

not insert

Debuging port

not used when Flash Memory

SST39VF040 Use only

DB[0…15]

MA[0

…

15]

XIN

MCLK

LD[0…7]

TP208

XIN

MRSTB

WRLL#

LCS3#

LOE#

LA[0…21]

+5VD

+3.65V

+3.65V

+3.65V

+5VD

+3.65V

+5VD

+5VD

+3.65V

+3.65V

+5VD

+5VD

3.2V

+3.65V

+5VD

C126

27p

C123

27p

R262

220

C129

27p

R120

4.7K

R122

RES

R270

220

R276

D201

1N5817

CE102

10

µ

/16V

R271

3.3K

R123

OPEN

U207F

74HC04

12

14

13

7

U207A

74HC04

2

14

1

7

U207B

74HC04

4

14

3

7

U207E

74HC04

10

14

11

7

U207C

74HC04

6

14

5

7

U207D

74HC04

8

14

9

7

C232

104

C234

104

J201

ROM EMULATOR

RESET

WE

1

3

CLK/CE1

ADDR/CE1

2

4

U201

W27E040/080

U102

KM416S1020CT-G07

21

22

23

24

27

28

29

30

31

32

20

19

35

34

18

17

16

15

14

36

33

37

1

50

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

DSCK

CS0#

RAS0#

CAS#

WE#

DQMX

2

3

5

6

8

9

11

12

39

40

42

43

45

46

48

49

7

13

4

10

38

44

41

47

25

26

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

U204

AT24C02A

VCC

NC

SCL

SDA

8

7

6

5

1

2

3

4

A0

A1

A2

VSS

TP105

U101

ES4318

105

24

173

174

175

176

198

199

170

204

205

206

207

2

3

4

5

6

7

10

11

12

13

14

15

16

19

20

21

22

23

178

179

180

181

182

185

186

187

188

189

190

191

194

195

196

197

145

150

149

143

142

146

151

152

153

144

154

155

158

122

123

124

125

126

127

128

131

132

133

134

135

136

137

140

141

47

47

47

47

47

47

47

47

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

R221

R224

R223

R222

R225

R226

R227

R220

R228

R229

R230

R204

R205

R206

R207

R208

R209

R210

R211

R212

R213

R214

R215

R216

R217

R218

R219

TP204

TP205

DRST#

DRD#

DWR#

DIORDY

DIOCS16#

DACS1#

DACS3#

DIRQ

DA0

DA1

DA2

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DRST#

DRD#

DWR#

DIORDY

DIOCS16#

DACS1#

DACS3#

DIRQ

DA[0…2]

DD[0…15]

39

40

32

33

36

37

38

47

46

45

41

42

116

117

119

118

106

107

108

109

110

113

114

115

100

97

72

73

74

69

71

70

101

102

53

54

55

56

57

58

61

62

63

64

65

66

77

78

79

80

87

82

85

86

87

88

89

90

93

94

95

96

160

161

162

165

166

167

168

169

49

50

48

31

25

28

30

29

171

172

177

183

184

192

193

200

201

208

1

8

9

17

18

26

27

203

202

34

35

43

44

51

52

TDMTSC

TDMDX/RSEL

TDMDR

TDMFS

TDMCLK

VSS

VCC

VSS

VCC

VSS

VSS

VCC

VSS

VCC

VSS

VCC

VSS

VCC

VSS

VCC

VSS

VCC

NC

NC

VSS

VCC

VSS

VCC

VCC

VSS

120

121

129

130

138

139

147

148

156

157

159

163

164

59

60

67

68

78

76

83

84

91

92

98

99

103

104

111

112

VSS

VCC

VSS

VCC

VSS

VCC

VSS

VCC

VSS

VCC

VPP

VSS

VCC

VCC

VSS

VSS

VCC

VCC

VSS

VCC

VSS

VSS

VCC

VSS

VCC

VSS

VCC

VCC

VSS

CLK

RESET

LCS0

LCS1

LCS2

LCS3

LWRLL

LWRHL

LOE

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LA18

LA19

LA20

LA21

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LD8

LD9

LD10

LD11

LD12

LD13

LD14

LD15

HRST

HRD/DCI_ACK

HWR/DCI_CLK

HRDQ

HWRQ/DCI_REQ

HIORDY

HIOCS16

HCS1FX

HCS3FX

HIRQ/DCI_ERR

HA0

HA1

HA2

HD0/DCI[0]

HD1/DCI[1]

HD2/DCI[2]

HD3/DCI[3]

HD4/DCI[4]

HD5/DCI[5]

HD6/DCI[6]

HD7/DCI[7]

HD8/DCI_FDS

HD9

HD10

HD11

HD12

HD13

HD14

HD15

RST#

LCS1#

LCS2#

LCS3#

WRLL#

LOE#

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LA18

LA19

LA20

LA21

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

MCLK

TBCK

TWS/SEL_PLL1

TSD0/SEL_PLL0

TSD1/SEL_PLL2

TSD2

TSD3

RBCK

RWS

RSD

SPDIF_DOBM

SPDIF_DIBM

PCLK2XSCN

PCLKQSCN

HSSCN

VSSCN

YUV0

YUV1

YUV2

YUV3

YUV4

YUV5

YUV6

YUV7

DCS0

DCS1

DRAS0

DRAS1

DRAS2

DCAS

DWE

DOE/DSCK_EN

DQM

DSCK

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

DMA9

DMA10

DMA11

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

AUX0

AUX1

AUX2

AUX3

AUX4

AUX5

AUX6

AUX7

XIN

XOUT

APLLCAP

YUV0

YUV1

YUV2

YUV3

YUV4

YUV5

YUV6

YUV7

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

I2C_DATA

I2C_CLK

HOST_DATA

VFD_DATA

VFD_STB

VFD_CLK

HOST_CLK

HOST_CS

I2C_DATA

I2C_CLK

HOST_DATA

VFD_DATA

VFD_STB

VFD_CLK

HOST_CLK

HOST_CS

C219

47p

C113

104

C114

104

C112

104

C220

104

C115

104

C218

104

C212

104

C213

104

C214

104

C215

104

C201

104

C202

104

C203

104

C204

104

C101

104

C102

104

C103

104

C205

104

C206

104

C207

104

C208

104

C209

104

C211

104

C104

104

C105

104

C106

104

C107

104

C108

104

C109

104

C110

104

C111

104

R129

47K

R121

4.7K

R130

47K

R273

R272

R277

1M

R203

0

R242

1K

R119

0

R241

1K

C128

104

R202

4.7K

R117

R116

R115

R113

R114

R118

R132

R101

R102

R103

R104

R105

R106

R107

R108

R109

R110

R111

R112

33

33

33

33

33

33

47

10

10

10

10

10

10

10

10

10

10

10

10

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

CS0#

CS1#

RAS0#

CAS#

WE#

DQMX

DSCK

R238

0

39LF040

U209

SST39VF040

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

20

19

18

17

16

15

14

13

3

2

31

1

12

4

5

11

10

6

9

D0

D1

D2

D3

D4

D5

D6

D7

VDD

VSS

WE

CE

OE

21

22

23

25

26

27

28

29

8

24

7

30

32

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

WRLL#

LCS3#

LOW#

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LA18

C210

104

TP206

TP207

TP201

TP202

R232

33

C127

open

CE201

10

µ

/16V

L201

FB2012

C122

27p

C124

27p

CE201

10

µ

/16V

C125

27p

R131

0

L202

FB2012

R261

1M

C227

33p

C228

22p

C229

33p

C230

open

C231

open

C233

104

U208A

74HC04

2

14

1

7

U208B

74HC04

4

14

3

7

U208C

74HC04

6

14

5

7

X201

27MHz

CE202

10

µ

/16V

R275

R274

open

0

open

open

0

YUV[0…7]

BCLK_DVD

LRCK_DVD

ASDATA_DVD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

CLK

CKE

CS

RAS

CAS

WE

DQML

DQMH

NC

NC

VCC

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCQ

VCCQ

VSSQ

VSSQ

VCCQ

VCCQ

VSSQ

VSSQ

VCC

VSS

TP101

TP102

TP103

TP104

HSYNC

VSYNC

MCLK

MRSTB

27MHZ

SPDIF

+3.65V

U103

KM416S1020CT-G07

21

22

23

24

27

28

29

30

31

32

20

19

35

34

18

17

16

15

14

36

33

37

1

50

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

DSCK

CS1#

RAS0#

CAS#

WE#

DQMX

2

3

5

6

8

9

11

12

39

40

42

43

45

46

48

49

7

13

4

10

38

44

41

47

25

26

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

C117

104

C118

104

C116

104

C119

104

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

CLK

CKE

CS

RAS

CAS

WE

DQML

DQMH

NC

NC

VCC

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCQ

VCCQ

VSSQ

VSSQ

VCCQ

VCCQ

VSSQ

VSSQ

VCC

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

CE

OE

D0

D1

D2

D3

D4

D5

D6

D7

VCC

GND

12

11

10

9

8

7

6

5

27

26

23

25

4

28

29

3

2

30

31

1

22

24

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LA18

LA19

LA21

13

14

15

17

18

19

20

21

32

16

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

TO MAIN CIRCUIT DIAGRAM (P. 2-11)

ª

Chassisplatte / Chassis Board – Audio/Video Decoder