M

ODEL

SDP100 V

ERSION

V_1.00

P

REPARED BY

H/W

D

ATE

25/05/2007

S

UBJECT

T

ECHNICAL

M

ANUAL

P

AGE

35/70

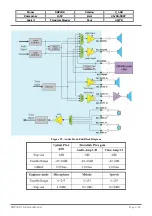

Figure 22. Touch Panel Driver IC circuit.

6.2

NAND Flash interface

MT6228 provides NAND flash interface. The NAND FLASH interface support features as follows:

-. ECC (Hamming code) acceleration capable of one-bit error correction or two bits error detection.

-. Programmable ECC block size. Support 1, 2 or 4 ECC block within a page.

-. Word/byte access through APB bus.

-. Direct Memory Access for massive data transfer.

-. Latch sensitive interrupt to indicate ready state for read, program, erase operation and error report.

-. Programmable wait states, command/address setup and hold time, read enable hold time, and write enable recovery time. -.

-. Support page size: 512(528) bytes and 2048(2112) bytes.

-. Support 2 chip select for NAND flash parts.

-. Support 8/16 bits I/O interface.

-. The NFI core can automatically generate ECC parity bits when programming or reading the device.

-. Used 7 control Signal : NRE#, NEW#,NCE#,NALE, WATCHDOG#,NCLE, NRNB.

In SDP100

, The Nand Flash Memory is used HYC0UEE0CF1 from Hynix. The HYC0UEE0CF1 is Nand Flash(512Mb) +

SDRAM (256Mb). The Figure 23 is shown the Circuit diagram. The I/O is 8bit interface from MT6228.

Figure 23. Hynix Nand MCP Circuit Diagram

6.3

USB Device controller

The MT6228 USB OTG controller complies with Universal Serial Bus (USB) Specification Rev 1.1 and USB On-The-Go

(OTG) Supplement Rev. 1.0a. The USB OTG controller supports USB device mode, USB simple host mode, as well as OTG

handshaking capabilities, at full-speed (12 Mbps) operation. The cellular phone uses this widely available USB interface to

exchange data with USB hosts such as a PC or laptop; or to function as a host, allowing it to connect to other devices. When

operating in host mode, only a single peer-to-peer (no intermediate hub) connection is supported.

SDP100

T

ECHNICAL

M

ANUAL

Page 3.35