M

ODEL

SDP100 V

ERSION

V_1.00

P

REPARED BY

H/W

D

ATE

25/05/2007

S

UBJECT

T

ECHNICAL

M

ANUAL

P

AGE

22/70

3.

Micro-Controller Unit Subsystem

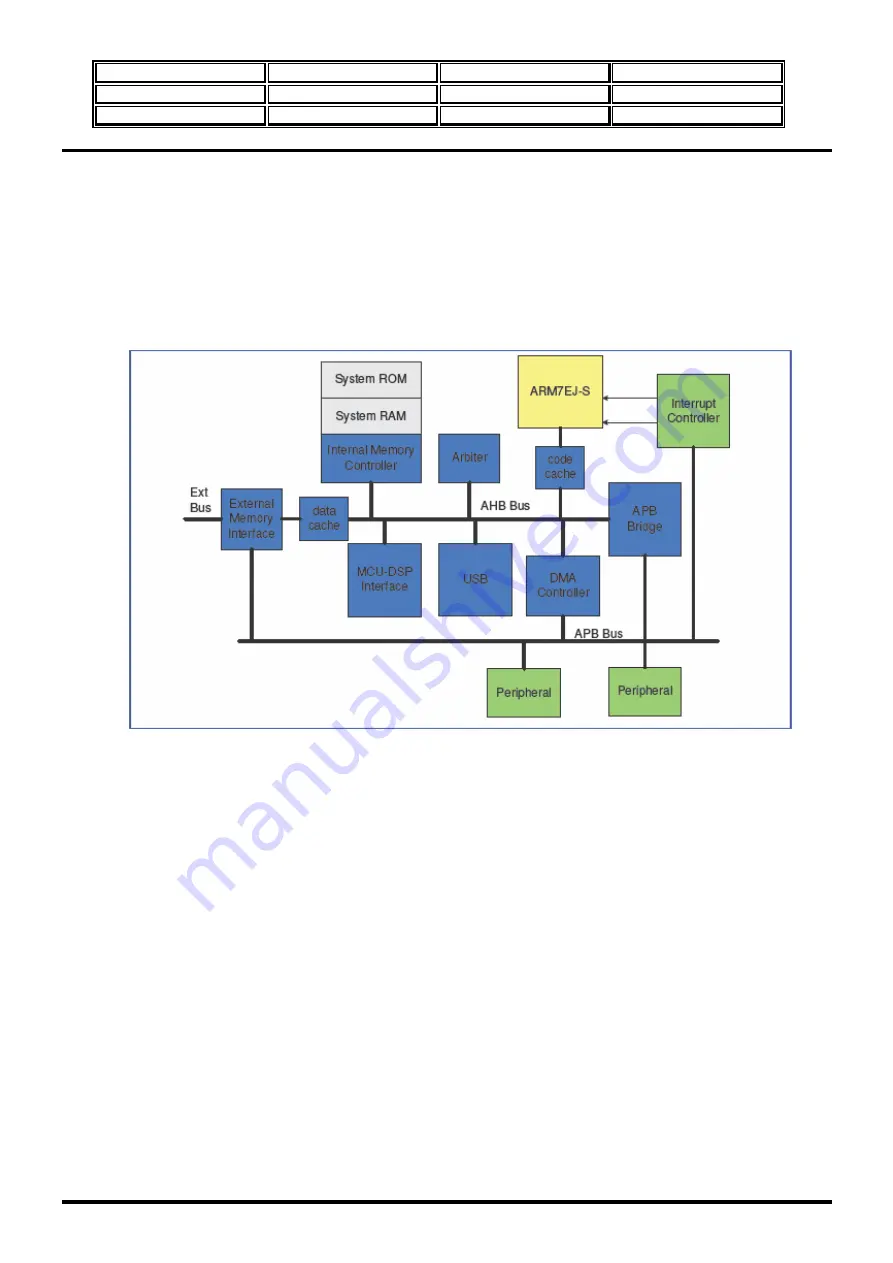

Figure 6 illustrates the block diagram of the Micro-Controller Unit Subsystem in MT6228. The Subsystem utilizes a

main 32-bit ARM7EJ-S RISC processor, which plays the role of the main bus master controlling the whole subsystem.

The processor communicates with all the other on-chip modules via the two-level system buses: AHB Bus and APB Bus.

All bus transactions originate from bus masters, while salves can only respond to requests from bus masters. Before data

transfer can be established, bus master must ask for bus ownership. This is accomplished by request-grant handshaking

protocol between masters and arbiters.

Figure 6. Block Diagram of MCU in MT6228

3.1

Processor Core

The Micro-Controller Unit subsystem in MT6228 uses the 32-bit Arm7EJ-S RISC processor that is based on the Von

Neumann architecture with a single 32-bit data bus carrying both instructions and data. The memory interface of

ARM7EJ-S is totally compliant to AMBA based bus system, which allows direct connection to the AHB Bus.

3.2

Memory Management

The processor core of MT6228 supports only memory addressing method for instruction fetch and data access. It

manages a 32bit address space that has addressing capability up to 4GB. System RAM, System ROM , Registers, MCU

Peripherals and external components are all mapped onto such 32-bit address space, as depicted in Figure 7.

SDP100

T

ECHNICAL

M

ANUAL

Page 3.22