CPC1001

C P C 1 0 0 1 U s e r M a n u a l

29

© 2 0 2 1 F a s t w e l V e r . 0 0 1

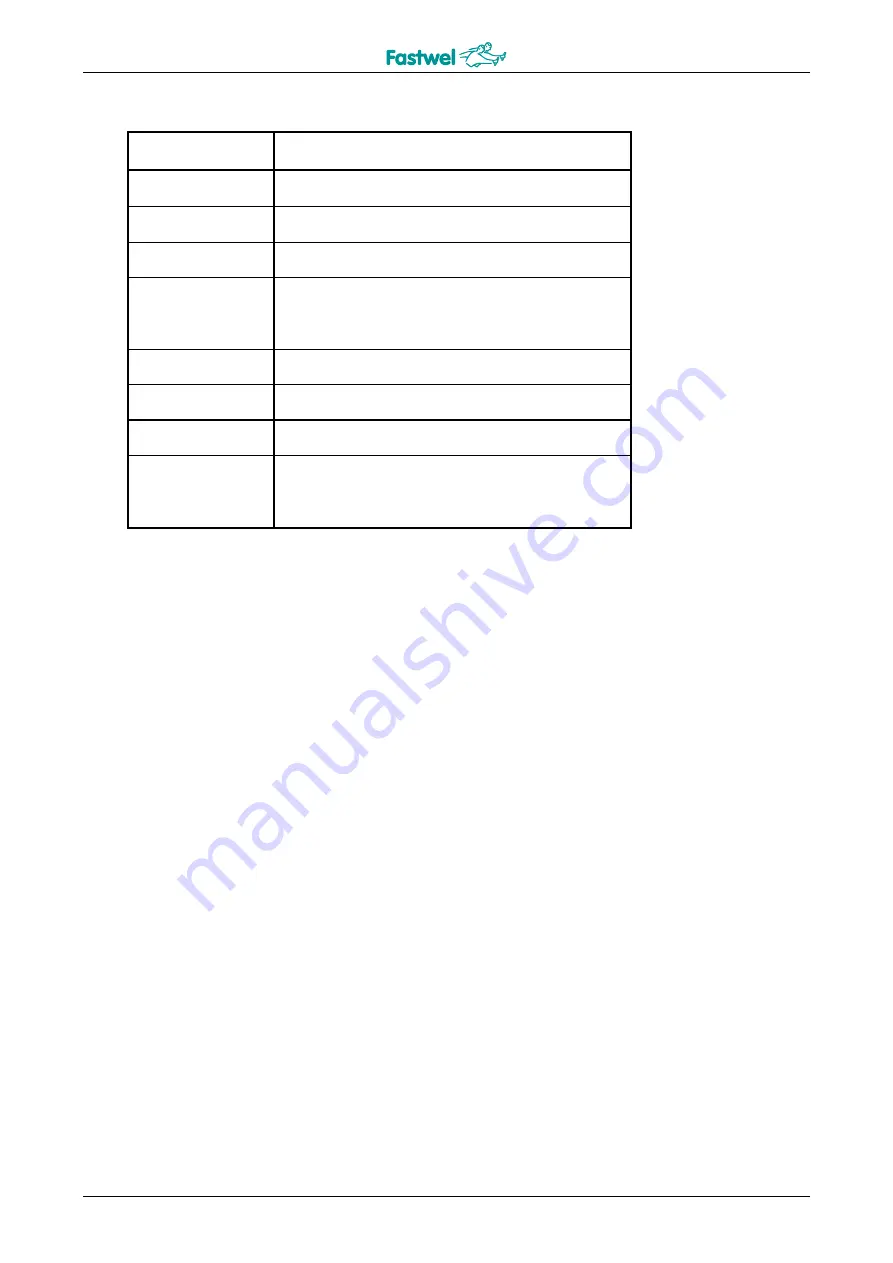

Table 2.2

– Boot sources of CPC1001

BOOT_SEL[2…0]#

OS boot source

000

SATA on the carrier board

001

SD card on the carrier board

(µSDHC2)

010

eMMC Flash on the carrier board

(µSDHC3)

011

SPI Flash on the carrier board (SPI0_CS1#)

EIM_D19 ALT1 ECSPI1_SS1 or ALT5

GPIO3_IO19

100

MMC-card on the carrier board

(µSDHC2)

101

Serial Boot (USB_OTG)

110

Onboard

eMMC Flash (µSDHC4)

111

Onboard SPI Flash (SPI0_CS0#)

EIM_EB2 ALT1 ECSPI1_SS0 or ALT5

GPIO2_IO30

BOOT_SEL [2… 0] # signals in CPC1001 have a pull-up, which ensures a high signal level (“1”)

where there are no external connections. To set the low level of signal

(“0”), the relevant circuit on

the carrier board must be grounded. The state of the BOOT_SEL [2 ... 0]# signals is considered

only at the time of the end of the CPC1001 hardware reset signal, therefore the selected source

will be saved during any further reboots initiated by the operating system or when the watchdog

timer is triggered.

For rebooting from the sources located on the carrier board, the corresponding devices must be

supplied with power by the time the boot starts. That is, it should not depend on the

CARRIER_PWR_ON and CARRIER_STBY# signals. The SDIO_PWR_EN signal, however,

can

be used to control power to the SD card on the carrier board.

2.7 Power up and down

The power is fed via the SMARC connector (subparagraph 1.6.2). Requirements to the supply

voltages of CPC1001 are given in Table 2.3.