Embedded Solutions

Page 17 of 46

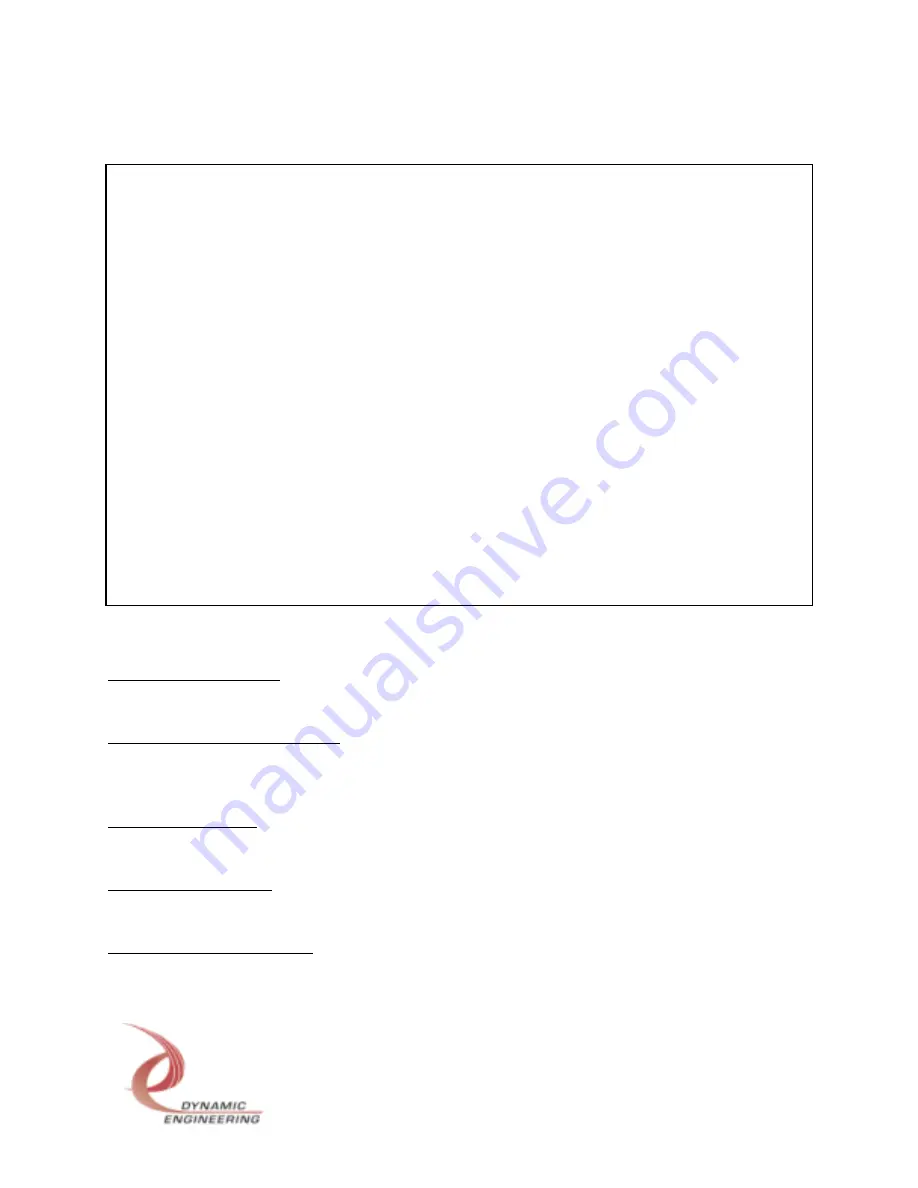

XM_CHAN0/1_STATUS

[0x0014, 0x0044] Channel Status Read / Latch Clear Write

Status Register

Data Bit

Description

31

INT_STAT

30-18

Spare

17

Virtex Interrupt Active

16

Local Interrupt Active

15

Read DMA Interrupt Active

14

Write DMA Interrupt Active

13

Read DMA Error

12

Write DMA Error

11-8

Spare

7

Receive FIFO Valid

6

Receive FIFO Full

5

Receive FIFO Almost Full

4

Receive FIFO Empty

3

Spare

2

Transmit FIFO Full

1

Transmit FIFO Almost Empty

0

Transmit FIFO Empty

FIGURE 7

PMC-XM SPARTAN3 CHANNEL STATUS REGISTER

Transmit FIFO Empty: When read as a ‘1’, the corresponding transmit FIFO is empty.

When read as a ‘0’, the FIFO has at least one word in it.

Transmit FIFO Almost Empty: : When read as a ‘1’, the corresponding transmit FIFO is

almost empty as determined by the value entered in the almost empty level register.

When read as a ‘0’, there is more data in the FIFO than specified in the level register.

Transmit FIFO Full: When read as a ‘1’, the corresponding transmit FIFO is full. When

read as a ‘0’, there is room for at least one more word in the FIFO.

Receive FIFO empty: When read as a ‘1’, the corresponding receive FIFO is empty.

When read as a ‘0’, the FIFO has at least one word in it.

Receive FIFO Almost Full: When read as a ‘1’, the corresponding receive FIFO is

almost full as determined by the value entered in the almost full level register. When

read as a ‘0’, there is less data in the FIFO than specified in the level register.