50

DS726PP2

CS4525

6.1.9

PWM Modulator Configuration

The CS4525 PWM modulators support flexible configuration options designed to simplify system integra-

tion. Delays may be inserted between the switching edges on adjacent channels to manage noise, and

the PWM switching frequency can be easily modified to eliminate interference with AM tuners.

6.1.9.1

PWM Channel Delay

The CS4525 includes a PWM output signal delay mechanism. This mechanism allows the PWM switching

edges to be offset between channels as a method of managing switching noise and reducing radiated

emissions.

The OutputDly[3:0] bits in the Output Cfg register are used to adjust the channel delay amount from

0 to 15 SYS_CLK or crystal input clock cycles, whichever is used as the input clock source. The absolute

delay time is calculated by multiplying the setting of the OutputDly[3:0] bits by the period of the input clock

source. By default, no delay is inserted.

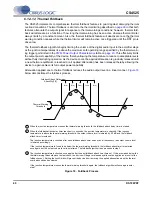

When the power outputs are configured for 2-channel full-bridge operation, the OUT3/OUT4 signal pair is

delayed from the OUT1/OUT2 signal pair by the delay amount as shown in

.

When the power outputs are configured for 3-channel (2-channel half-bridge and 1-channel full-bridge)

operation, OUT2 is delayed from OUT1 by the delay amount, and the OUT3/OUT4 pair is delayed from

OUT2 by the delay amount as shown in

The OutputDly[3:0] bits can only be changed when all modulators and associated logic are in the power-

down state by setting the PDnAll bit. Attempts to write these bits while the PDnAll bit is cleared will be

ignored.

Referenced Control

Register Location

OutputDly[3:0] .....................

“Channel Delay Settings (OutputDly[3:0])” on page 73

OUT1

OUT2

tch

dly

OUT3

OUT4

Figure 20. 2-Channel Full-Bridge PWM Output Delay

OUT1

OUT2

tch

dly

tch

dly

OUT3

OUT4

Figure 21. 3-Channel PWM Output Delay